## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PARIS VI

## Spécialité : INFORMATIQUE ET MICRO-ÉLECTRONIQUE

Présentée par : Mohamed DESSOUKY

Pour obtenir le titre de Docteur de l'Université Paris VI

# Conception en vue de la Réutilisation de Circuits Analogiques. Application: Modulateur Delta-Sigma à très Faible Tension

Soutenue le : 18 Janvier 2001

Devant le jury composé de :

| M. Georges GIELEN          | Rapporteur  |

|----------------------------|-------------|

| M. Patrice SENN            | Rapporteur  |

| M. Andreas KAISER          | Examinateur |

| M. Hani RAGAI              | Examinateur |

| M. Yves LEDUC              | Examinateur |

| M. Alain GREINER           | Examinateur |

| Mme. Marie-Minerve LOUERAT | Examinateur |

## Ph.D. THESIS OF THE UNIVERSITY OF PARIS VI

Department : COMPUTER SCIENCE AND MICRO-ELECTRONICS

Presented by : Mohamed DESSOUKY

Thesis submitted to obtain the degree of **DOCTOR OF THE UNIVERSITY OF PARIS VI**

## DESIGN FOR REUSE OF ANALOG CIRCUITS. CASE STUDY: VERY LOW-VOLTAGE DELTA-SIGMA MODULATOR

18 January 2001

Committee in charge :

M. Georges GIELEN

M. Patrice SENN

M. Andreas KAISER

M. Hani RAGAI

M. Yves LEDUC

M. Alain GREINER

Mme. Marie-Minerve LOUERAT

À la mémoire de ma mère.

# Remerciements

Je tiens tout d'abord à remercier Madame Marie-Minerve Louërat, Chargée de Recherche CNRS au laboratoire LIP6, d'avoir dirigé mes recherches et d'avoir organisé avec efficacité les contacts avec les autres équipes hors du laboratoire. Je lui suis très reconnaissant pour ses qualités rares tant au niveau humain que scientifique sans lesquels le développement et l'achèvement de ces recherches - et de ce manuscrit - n'auraient été possibles.

Je tiens particulièrement à remercier le professeur Alain Greiner à la fois pour son travail d'encadrement, ses conseils, sa patiente relecture du manuscrit et ses qualités pédagogiques que j'apprécie beaucoup.

Je tiens à remercier vivement Monsieur Andreas Kaiser, Chargé de Recherche CNRS et professeur à l'ISEN-Lille, pour m'avoir accueilli au sein de son équipe pendant la phase de conception et de mesure du circuit. Je lui dois beaucoup, entre autres, pour les nombreuses et instructives discussions.

Je remercie également Monsieur Jacky Porte, Ingénieur d'étude à l'ENST-Paris, pour m'avoir permis d'utiliser son logiciel COMDIAC et pour les enrichissantes discussions que nous avons eu.

Que les membres du jury trouvent ici l'expression de ma gratitude. Tout d'abord, le professeur Georges Gielen, Responsable de l'équipe de Méthodologies de Conception de circuits analogiques et mixtes dans le groupe MICAS à l'Université Catholique de Leuven, Belgique, et Monsieur Patrice Senn, Responsable du laboratoire France Telecom R&D/DIH/OCF, qui m'ont fait l'honneur d'être rapporteurs de cette thèse. Le professeur Hani Ragai Responsable du laboratoire ICL au département d'Electroniques et Télécommunications, Université d'Ain Shams, Egypte, et Monsieur Yves Leduc, de Texas Instruments, pour l'intérêt qu'ils ont porté à mes travaux de recherches.

Je remercie tous les membres de l'équipe ASIM du laboratoire LIP6, et plus particulièrement Abdelhakim Khouas pour son soutien et son amitié pendant ces années, Hassan Aboushady pour les innombrables conversations et "deadlines" que nous avons vécu ensemble, Frédéric Pétrot, Franck Wajsbürt, et Ludovic Jacomme pour m'avoir aidé à comprendre et à utiliser avec efficacité les outils ALLIANCE. Je remercie également tous les étudiants de DEA qui ont contribué à l'évolution de l'outil CAIRO : Ronan Lucas, Frédéric Billereau, Alphonse Chesneau et plus particulièrement Matthieu Lintz et Pierre Nguyen Tuong à qui je souhaite une bonne continuation dans leurs recherches.

Je ne pourrai jamais trouver les mots justes pour exprimer mes sentiments pour ma meilleure amie et sœur Naglaa. Je veux la remercier pour son soutien, ses sacrifices et surtout pour m'avoir toujours cru à chaque fois que je lui disais que je finirai la thèse "l'année prochaine".

Enfin, je ne connais personne qui aurait été plus heureuse d'assister à l'achèvement de cette thèse, et à qui je pensais constamment pendant ces dernières années, que ma mère. Si j'ai eu de la patience, de la volonté et de la persévérance qui m'ont permis de mener ce travail, ce n'étaient que quelque gouttes que j'ai pu récupérer de la rivière abondante de sa vie. Si elle a dû quitter ce monde au milieu de la thèse, son esprit restera présent en moi à tout jamais.

M. Dessouky

# Résumé

Le fait de pouvoir réutiliser des circuits analogiques pour différents procédés cibles prend de plus en plus d'importance dans la conception des systèmes intégrés actuels. Pour atteindre les meilleures performances en changeant de technologie cible, un des problèmes clés est la prise en compte des dégradations possibles dues aux masques physiques dans la phase de synthèse électrique.

Pour résoudre ce problème, nous avons proposé une nouvelle méthode de conception, basée sur la synthèse analogique prenant en compte le dessin des masques. Cette méthode permet de conserver le savoir-faire pour une réutilisation future tout en assurant une forte intégration entre la phase du dimensionnement électrique et la réalisation physique. Elle garantit le respect des performances attendues, permet d'optimiser certains aspects de la conception en présence de parasites et réduit le temps total de conception en évitant les itérations fastidieuses entre le dimensionnement et les masques. Cette méthode a été mise en oeuvre grâce à deux outils basés sur le savoir-faire, l'un dédié au dimensionnement des circuits analogiques (COMDIAC) et l'autre au dessin des masques (CAIRO). Ces outils permettent de réutiliser de manière efficace la méthode de conception ainsi que le dessin des masques dans le cas de circuits similaires.

Pour valider cette approche, nous l'avons appliquée à des circuits basse-tension, basseconsommation. Notre étude a conduit à de nouvelles architectures de circuits qui permettent le fonctionnement sous très basse tension d'un circuit à capacités commutées en technologie CMOS standard. En suivant cette approche, nous avons conçu, fabriqué et testé un modulateur analogique-numérique Delta- Sigma pour des applications numériques audio, fonctionnant sous 1V avec 14 bits de précision. Deux circuits similaires ont été resynthétisés dans une autre technologie cible, montrant ainsi que notre méthode est tout à fait appropriée pour des circuits mixtes analogiques-numériques à hautes performances.

#### Mots Clés

Circuits analogiques réutilisables, Automatisation de la conception analogique, Génération de masques procédurale, Modulation Delta-Sigma, Basse-tension, Capacités commutées.

## Abstract

Analog design reuse is becoming more and more important in recent system-on-chip designs. In these designs electrical and physical design integration is a challenging problem specially when designing high performance analog circuits in different technologies.

To solve this problem, we propose a new design methodology based on a layout-oriented synthesis approach that allows to capture design knowledge for eventual reuse with a close interaction between electrical and physical design. This methodology guarantees the fulfillment of the required performance specifications, permits to optimize various design aspects in the presence of parasitics and shortens the overall design time by avoiding laborious sizing-layout iterations. The methodology has been implemented using two knowledge-based tools dedicated to analog circuit sizing (COMDIAC) and layout generation (CAIRO). The tools allow both the design knowledge and the generated layout to be efficiently reused in similar designs.

To validate the previous claims, we have chosen low-voltage low-power analog circuits as an application. Our study has led to new circuit architectures that allow very low-voltage switched-capacitor circuit operation in standard CMOS technologies. Using the above methodology and circuit techniques, we have designed, fabricated, and tested a 1-V 14-bit Delta-Sigma A/D modulator for digital-audio applications. Two similar designs are then resynthesized in another technology demonstrating the suitability of the methodology for very high performance mixed-signal circuits.

#### Keywords

Analog Design Reuse, Analog Design Automation, Procedural Layout Generation, Delta-Sigma Modulator, Low-Voltage, Switched-Capacitor.

# Contents

|   | Remerciements |                                           |      | i            |  |  |  |

|---|---------------|-------------------------------------------|------|--------------|--|--|--|

|   | Rés           | umé                                       | iii  |              |  |  |  |

|   | Abstract      |                                           |      | $\mathbf{v}$ |  |  |  |

|   | Contents      |                                           |      | vii          |  |  |  |

|   | List          | t of Abbreviations and Symbols            | xiii |              |  |  |  |

|   | List          | t of Figures                              | xvii |              |  |  |  |

|   | List          | t of Tables                               | 3    | xxi          |  |  |  |

|   | Rés           | umé Étendu en Français                    | xx   | iii          |  |  |  |

| 1 | Intr          | roduction                                 |      | 1            |  |  |  |

|   | 1.1           | Motivation                                |      | 1            |  |  |  |

|   | 1.2           | Contribution                              |      | 2            |  |  |  |

|   | 1.3           | Outline                                   |      | 4            |  |  |  |

| 2 | Pro           | blem Definition and Motivation            |      | 5            |  |  |  |

|   | 2.1           | Introduction                              |      | 5            |  |  |  |

|   | 2.2           | Analog Design Particularities             | •    | 5            |  |  |  |

|   | 2.3           | IP and Analog Cores                       | •    | 7            |  |  |  |

|   | 2.4           | Design Automation and Design Reuse        |      | 9            |  |  |  |

|   | 2.5           | Very Low-voltage $\Delta\Sigma$ Modulator |      | 10           |  |  |  |

|   | 2.6           | Work Objectives                           |      | 11           |  |  |  |

| 3 | Stat          | te of the Art                             |      | 13           |  |  |  |

|   | 3.1           | Introduction                              | •    | 13           |  |  |  |

|   | 3.2           | The Mixed-Signal Design Process           | •    | 13           |  |  |  |

|   |               | 3.2.1 System Sizing                       |      | 14           |  |  |  |

|   |      | 3.2.2 Block Sizing                                       | 5  |

|---|------|----------------------------------------------------------|----|

|   |      | 3.2.3 Cell Sizing                                        | 6  |

|   |      | 3.2.4 Cell Layout                                        | 8  |

|   |      | 3.2.5 Block Layout                                       | 9  |

|   |      | 3.2.6 System Layout                                      | 9  |

|   | 3.3  | Layout Parasitics Control                                | 20 |

|   | 3.4  | Analog IP and Technology Migration                       | 21 |

|   | 3.5  | Conclusions                                              | 3  |

| 4 | Lay  | out-Oriented Design Methodology 2                        | 25 |

|   | 4.1  | Introduction                                             | 25 |

|   | 4.2  | Analog Design Reuse                                      | 25 |

|   | 4.3  | Layout-Oriented Design Methodology                       | :6 |

|   | 4.4  | Advantages                                               | 51 |

|   | 4.5  | Top-Down or Bottom-Up                                    | 2  |

|   | 4.6  | Conclusions                                              | 3  |

| 5 | Proc | cedural Layout with Parasitics Calculation 3             | 5  |

|   | 5.1  | Introduction                                             | 5  |

|   | 5.2  | Overview                                                 | 5  |

|   | 5.3  | Device Generators                                        | 57 |

|   | 5.4  | Analog Layout Constraints                                | 0  |

|   |      | 5.4.1 Parasitics Constraints                             | 0  |

|   |      | 5.4.2 Matching Constraints                               | 2  |

|   |      | 5.4.3 Reliability Constraints                            | .5 |

|   | 5.5  | Hierarchical Placement                                   | .7 |

|   | 5.6  | Area Optimization                                        | 8  |

|   |      | 5.6.1 Shape Functions                                    | 8  |

|   |      | 5.6.2 Slice Area Optimization                            | 9  |

|   |      | 5.6.3 Module Area Optimization                           | 51 |

|   |      | 5.6.4 Multilevel Hierarchical Top-Down Area Optimization | 51 |

|   | 5.7  | Routing                                                  | 52 |

|   | 5.8  | Parasitics Extraction                                    | 53 |

|   |      | 5.8.1 Device parasitics                                  | 53 |

|   |      | 5.8.2 Routing capacitance                                | 54 |

|   | 5.9  | Fabrication Process Independence                         | 55 |

|   |      | 5.9.1 Symbolic Layout Approach                           | 5  |

|   |      | 5.9.2 Symbolic Layout for Analog Circuits                | 55 |

|   |      | 5.9.3 Limitations                                        | 6  |

### CONTENTS

|       | 5.10       | Example                                             |

|-------|------------|-----------------------------------------------------|

|       | 5.11       | Conclusions                                         |

| 6     | <b>C</b> ' |                                                     |

| 6     |            | uit Sizing with Layout Parasitics 63                |

|       | 6.1        | Introduction                                        |

|       | 6.2        | Sizing Approach                                     |

|       | 6.3        | Sizing Procedure                                    |

|       |            | 6.3.1 Device Sizing                                 |

|       |            | 6.3.2 Sub-circuit Sizing                            |

|       |            | 6.3.3 OTA Sizing                                    |

|       |            | 6.3.4 Interactive Graphical Interface               |

|       | 6.4        | Impact of Parasitics                                |

|       | 6.5        | Conclusions                                         |

| 7     | Low        | -voltage Switched-Capacitor Circuit Design 77       |

|       | 7.1        | Introduction                                        |

|       | 7.2        | Low-voltage Switched-Capacitor Problems             |

|       | 7.3        | Proposed Technique                                  |

|       |            | 7.3.1 The Charge Cancellation Scheme                |

|       |            | 7.3.2 The Double Reference Voltage Scheme           |

|       | 7.4        | Low-voltage Bootstrapped Switch                     |

|       | 7.5        | Low-voltage Opamp                                   |

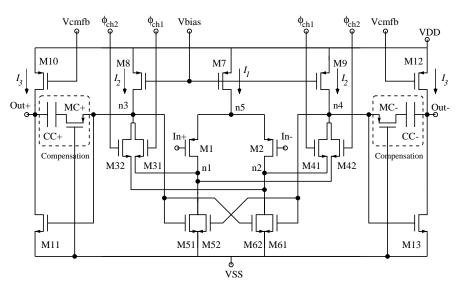

|       |            | 7.5.1 Opamp Structure                               |

|       |            | 7.5.2 Common-Mode Feedback                          |

|       |            | 7.5.3 Opamp Compensation                            |

|       |            | 7.5.4 Noise Reduction                               |

|       |            | 7.5.5 Simulation Results                            |

|       | 7.6        | Conclusions                                         |

|       |            |                                                     |

| 8     |            | ign of a Very Low-voltage Delta-Sigma Modulator 101 |

|       | 8.1        | Introduction                                        |

| 8.2 N |            | Methodology and Tools                               |

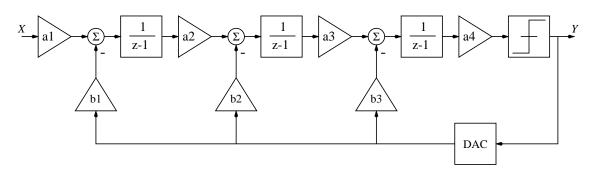

|       | 8.3        | High-Level Synthesis                                |

|       |            | 8.3.1 Performance Goal                              |

|       |            | 8.3.2 Coefficient Determination                     |

|       | 8.4        | Performance Parameter Mapping                       |

|       |            | 8.4.1 Opamp Finite Gain and Frequency Performance   |

|       |            | 8.4.2 Opamp Slew Rate                               |

|       |            | 8.4.3 Comparator Offset and Hysteresis              |

|    | 8.5  | Low-I   | evel Synthesis and Design                         |

|----|------|---------|---------------------------------------------------|

|    |      | 8.5.1   | Switched-Capacitor Implementation                 |

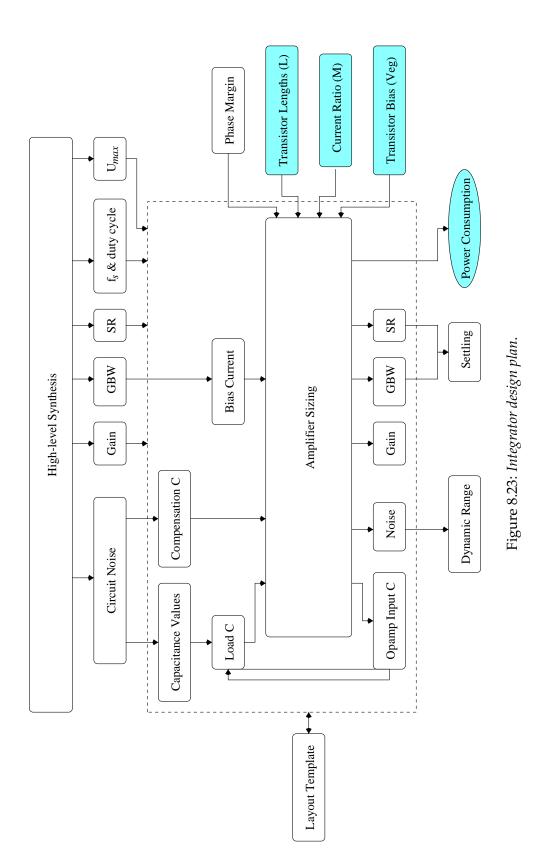

|    |      | 8.5.2   | Integrator Synthesis                              |

|    |      |         | 8.5.2.1 Noise and Dynamic Range Calculation       |

|    |      |         | 8.5.2.2 Opamp Synthesis                           |

|    |      |         | 8.5.2.3 Integrator Sizing in COMDIAC              |

|    |      | 8.5.3   | Switch Synthesis                                  |

|    |      |         | 8.5.3.1 Integrator Switch Synthesis               |

|    |      |         | 8.5.3.2 Switch Sizing in COMDIAC                  |

|    |      |         | 8.5.3.3 Bootstrapped Switch Sizing                |

|    |      | 8.5.4   | Comparator-Latch Design                           |

|    | 8.6  | Concl   | usions                                            |

| 9  | Prot | otvne l | mplementation 143                                 |

| ,  | 9.1  |         | uction                                            |

|    | 9.2  |         | cal Design                                        |

|    |      | 9.2.1   | Bias                                              |

|    |      | 9.2.2   | Clock Generation                                  |

|    | 9.3  |         | cal Design                                        |

|    |      | 9.3.1   | Technology                                        |

|    |      | 9.3.2   | Layout                                            |

|    | 9.4  | Exper   | imental Results                                   |

|    |      | 9.4.1   | Test Setup                                        |

|    |      | 9.4.2   | Measurement Results                               |

|    |      | 9.4.3   | Performance Comparison                            |

|    | 9.5  | Desig   | n Reuse                                           |

|    |      | 9.5.1   | Another Process Technology                        |

|    |      | 9.5.2   | Process Migration of the Same Modulator           |

|    |      | 9.5.3   | Fourth-Order Modulator                            |

|    | 9.6  | Concl   | usions                                            |

| 10 | Car  | -1      | and Estrum Directions 1/5                         |

| 10 |      |         | and Future Directions         165           usion |

|    |      |         | e Work                                            |

|    | 10.2 | Future  | e work                                            |

| A  | CAI  | RO Lag  | yout Language Syntax 169                          |

|    | A.1  | Modu    | le Definition                                     |

|    | A.2  | Availa  | ble Devices                                       |

|    |      | A.2.1   | TRANSISTOR                                        |

|   | A.2.1.1 Transistor Layout Options                                   | 171 |

|---|---------------------------------------------------------------------|-----|

|   | A.2.2 DIFFPAIR                                                      | 172 |

|   | A.2.3 BIASPAIR                                                      | 172 |

|   | A.2.4 CURRENT_MIRROR                                                | 173 |

|   | A.2.5 CAPACITOR                                                     | 174 |

|   | A.2.6 CAPACITOR MATRIX                                              | 175 |

|   | A.2.7 RESISTOR                                                      | 175 |

|   | A.2.8 BLACK BOX                                                     | 176 |

|   | 3 The Hierarchy                                                     | 176 |

|   | .4 Area Optimization                                                | 178 |

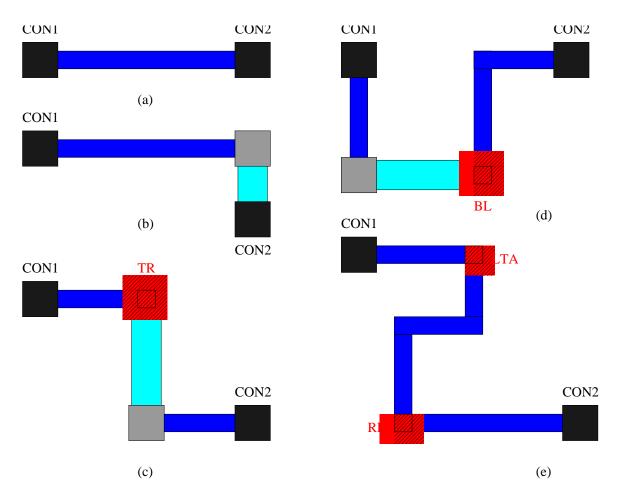

|   | 5 Routing                                                           | 180 |

|   | A.5.1 Definition of Module Connectors                               | 184 |

|   | A.5.2 Capturing Relative Coordinates                                | 188 |

|   | .6 Technology Variables                                             | 189 |

|   | 7 Design Rule Check and Layout Statistics                           | 190 |

|   | .8 Related Files                                                    | 190 |

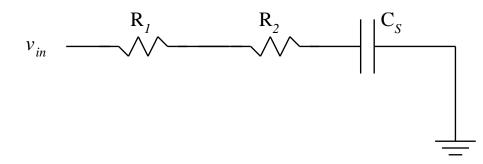

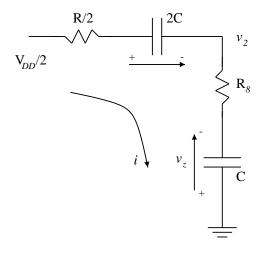

| B | oltage Transients in <i>R-C</i> Networks                            | 193 |

|   | .1 <i>R-C-C</i> Network                                             | 193 |

|   | .2 Analysis of Voltage Transients in the Charge Cancellation Scheme | 194 |

|   | ist of Publications                                                 | 197 |

|   | Bibliography                                                        |     |

# List of Abbreviations and Symbols

## Abbreviations

| AC    | Alternating Current.                            |

|-------|-------------------------------------------------|

| ADC   | Analog-to-Digital Converter.                    |

| BS    | Bootstrapped Switch.                            |

| BW    | Bandwidth.                                      |

| CAD   | Computer-Aided Design.                          |

| СМ    | Common-mode.                                    |

| CMFB  | Common-mode Feedback.                           |

| CMOS  | Complementary Metal Oxide Semiconductor.        |

| DAC   | Digital-to-Analog Converter.                    |

| DA    | Design Automation.                              |

| DC    | Direct Current.                                 |

| DR    | Dynamic Range.                                  |

| EDA   | Electronic Design Automation.                   |

| FM    | Figure of Merit.                                |

| GBW   | Gain-Bandwidth product.                         |

| HDL   | Hardware Design Language.                       |

| IP    | Intellectual Property.                          |

| IC    | Integrated circuit.                             |

| MOS   | Metal Oxide Semiconductor.                      |

| NTF   | Noise Transfer Function.                        |

| Opamp | Operational Amplifier.                          |

| OSR   | Oversampling Ratio.                             |

| OTA   | Operational Transconducatne Amplifier.          |

| SC    | Switched-capacitor.                             |

| SO    | Switched-opamp.                                 |

| SoC   | System-on-Chip.                                 |

| SNR   | Signal-to-Noise Ratio.                          |

| SNDR  | Signal-to-Noise plus Harmonic Distortion Ratio. |

|       |                                                 |

| SQNR | Signal-to-Quantization Noise Ratio.                               |

|------|-------------------------------------------------------------------|

| SR   | Slew Rate.                                                        |

| PM   | Phase Margin.                                                     |

| PSRR | Power Supply Rejection Ratio.                                     |

| VHDL | Very High Speed Integrated Circuit Hardware Description Language. |

| VLSI | Very Large Scale Integration.                                     |

| VM   | Voltage Multiplication.                                           |

## Symbols

| $A_{d0}$       | Opamp DC gain.                                                    |

|----------------|-------------------------------------------------------------------|

| $eta_i$        | Integrator feedback factor (integration phase).                   |

| $\beta_s$      | Integrator feedback factor (sampling phase).                      |

| $C_C$          | Opamp compensation capacitance.                                   |

| $C_{ip}$       | Opamp input capacitance.                                          |

| $C_I$          | Integration capacitance.                                          |

| $C_{Ibp}$      | Integration capacitor parasitic bottom-plate capacitance.         |

| $C_{ds}$       | Transistor Drain-source capacitance.                              |

| $C_{db}$       | Transistor Drain-bulk junction capacitance.                       |

| $C_{sb}$       | Transistor Source-bulk junction capacitance.                      |

| $C_{gb}$       | Transistor Gate-bulk capacitance.                                 |

| $C_{gd}$       | Transistor Gate-drain capacitance.                                |

| $C_{gs}$       | Transistor Gate-source capacitance.                               |

| $C_L$          | Opamp load capacitance.                                           |

| $C_{ox}$       | Transistor oxide capacitance.                                     |

| $C_S$          | Sampling capacitance.                                             |

| $\mathfrak{F}$ | Transistor diffusion capacitance reduction factor due to folding. |

| $f_{CL}$       | Opamp closed-loop 3-dB frequency.                                 |

| $f_l$          | Lowest signal frequency (=200Hz).                                 |

| $f_m$          | Maximum signal frequency (signal bandwidth).                      |

| $f_s$          | Sampling frequency.                                               |

| $f_t$          | Opamp gain-bandwidth product frequency.                           |

| $f_u$          | Opamp unity-gain frequency.                                       |

| $\phi_j$       | pn junction built-in potential.                                   |

| $g_0$          | Integrator gain.                                                  |

| $g_{ds}$       | Drain-source conductance.                                         |

| $g_m$          | Input-output transconductance.                                    |

| $g_{mb}$       | Bulk transconductance.                                            |

|                |                                                                   |

### LIST OF ABBREVIATIONS AND SYMBOLS

| $g_o$            | Output conductance.                                                           |

|------------------|-------------------------------------------------------------------------------|

| $\gamma_{th}$    | White noise excess factor.                                                    |

| $\gamma_{f}$     | Flicker noise excess factor.                                                  |

| $\theta_i$       | Settling error in the integration phase.                                      |

| $I_D$            | Transistor drain-source current.                                              |

| $I_{Dsat}$       | Transistor drain-source current.                                              |

| k                | Boltzman constant.                                                            |

| $\lambda$        | Symbolic layout unit.                                                         |

| M                | Number of parallel transistor elements of a given transistor.                 |

| $N_T$            | Total noise power.                                                            |

| $N_Q$            | Quantization noise power.                                                     |

| $N_{sw}$         | Switches noise or $KT/C$ noise power.                                         |

| $N_{amp}$        | Total opamp noise power.                                                      |

| $N_{th}$         | Opamp thermal noise power.                                                    |

| $N_{1/f}$        | Opamp flicker noise power.                                                    |

| $NTF_{inf}$      | Out-of-band gain of the noise transfer function.                              |

| $ ho_i$          | Closed-loop static error (integration phase).                                 |

| $ ho_s$          | Closed-loop static error (sampling phase).                                    |

| T                | Absolute Temperature.                                                         |

| $T_s$            | Sampling period.                                                              |

| $t_s$            | Time allowed for sampling.                                                    |

| $t_i$            | Time allowed for integration.                                                 |

| $t_{av}$         | Available time for charging/discharging.                                      |

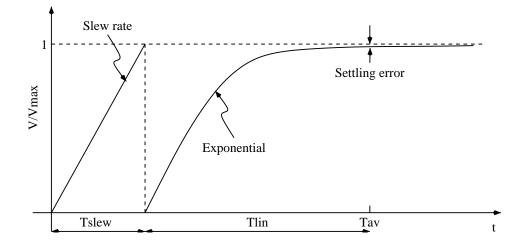

| $t_{lin}$        | Time of linear response.                                                      |

| $t_{nov}$        | Non-overlap clock phases time.                                                |

| $t_{slew}$       | Time of slewing response.                                                     |

| au               | Integrator time constant.                                                     |

| $	au_{cmfb}$     | Opamp CMFB time constant.                                                     |

| $\omega_t$       | Gain-bandwith product.                                                        |

| $\omega_{tcmfb}$ | Gain-bandwith product of the CMFB amplifier.                                  |

| $\omega_u$       | Unity gain frequency.                                                         |

| $U_{max}$        | Maximium allowable input signal level for which the modulator remains stable. |

| $\mu$            | Transistor channel mobility.                                                  |

| $V_{AGND}$       | Analog ground common-mode voltage.                                            |

| $V_{bias}$       | Transistor bias voltage.                                                      |

| $Vb_{cmfb}$      | Transistor CMFB circuit bias voltage.                                         |

| $V_{BS}$         | Transistor bulk-source voltage.                                               |

| $V_{DD}$         | Supply voltage.                                                               |

\_\_\_\_

### LIST OF ABBREVIATIONS AND SYMBOLS

| $V_D$         | Transistor drain voltage.                                      |

|---------------|----------------------------------------------------------------|

| $V_{DS}$      | Transistor drain-source voltage.                               |

| $V_{dsat}$    | Transistor saturation voltage.                                 |

| $V_E$         | Transistor Early voltage.                                      |

| $V_{EG}$      | Transistor effective gate-source voltage $(V_{GS} - V_{th})$ . |

| $V_{GS}$      | Transistor gate-source voltage.                                |

| $V_{th}$      | Transistor threshold voltage.                                  |

| $Vip_{CM}$    | Opamp input common-mode voltage.                               |

| $Vop_{CM}$    | Opamp output common-mode voltage.                              |

| $Vop_{max}$   | Opamp maximum output voltage.                                  |

| $Vop_{min}$   | Opamp minimum output voltage.                                  |

| $Vop_{swing}$ | Opamp linear output voltage swing.                             |

| $V_{ref}$     | Modulator reference voltage.                                   |

| $V_S$         | Transistor source voltage.                                     |

| $V_{SS}$      | Supply ground voltage.                                         |

|               |                                                                |

# **List of Figures**

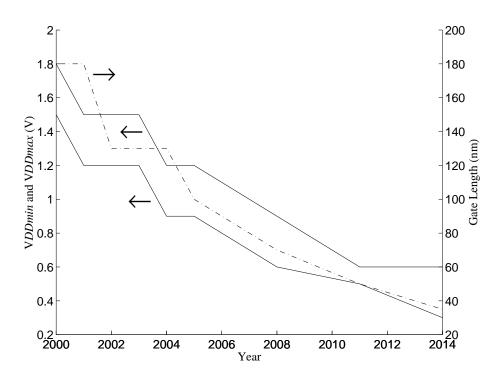

| 2.1  | Power supply and Gate length evolution                                                | 10 |

|------|---------------------------------------------------------------------------------------|----|

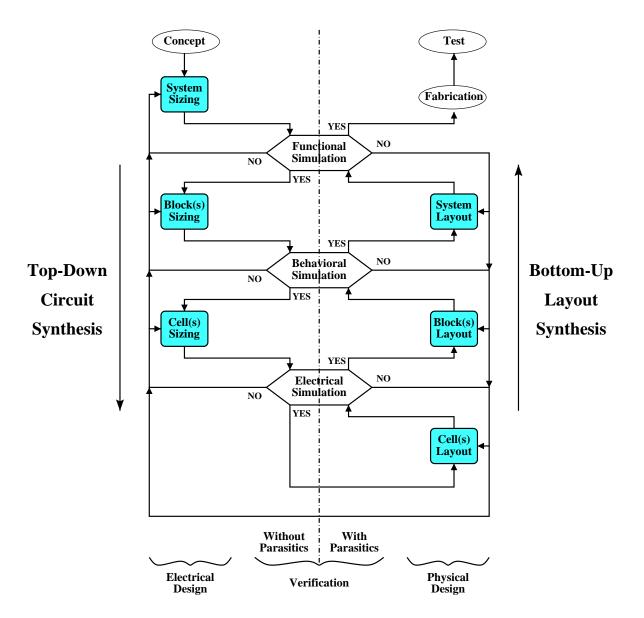

| 3.1  | Mixed-signal design process                                                           | 14 |

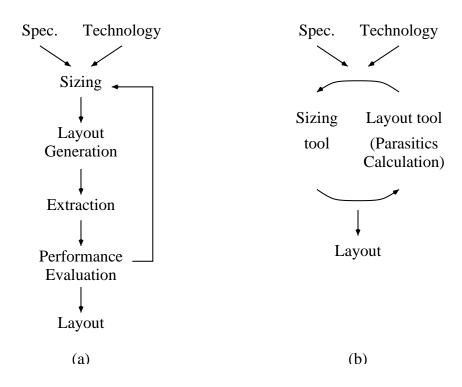

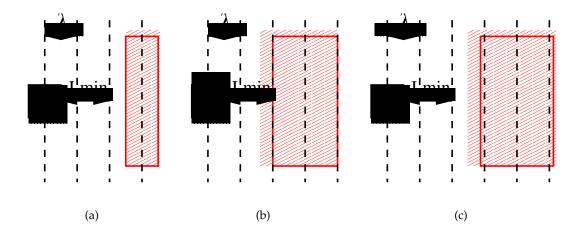

| 4.1  | Parasitics Compensation Methodology: (a) traditional and (b) proposed                 | 27 |

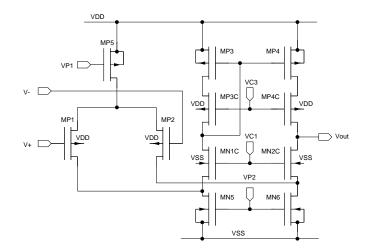

| 4.2  | Schematic template: Folded cascode OTA                                                | 28 |

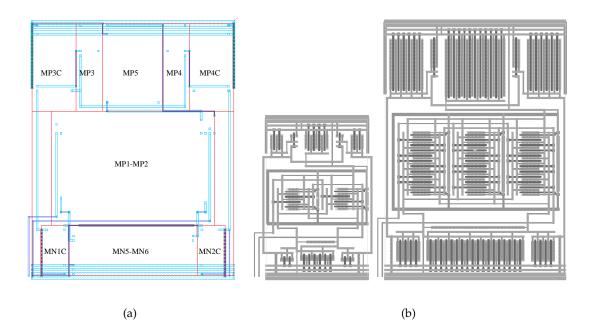

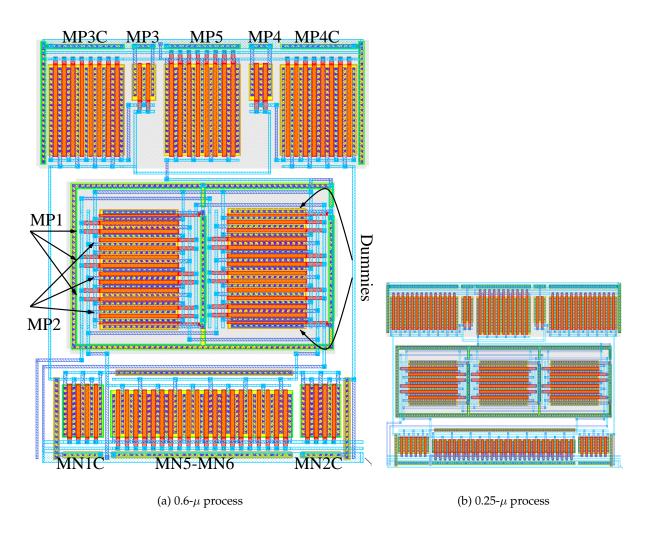

| 4.3  | (a) Layout template and (b) two generated layouts for the folded cascode OTA $\ldots$ | 28 |

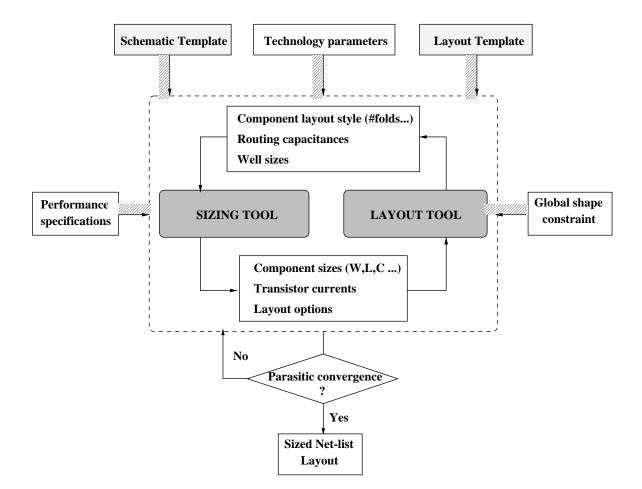

| 4.4  | The proposed methodology                                                              | 29 |

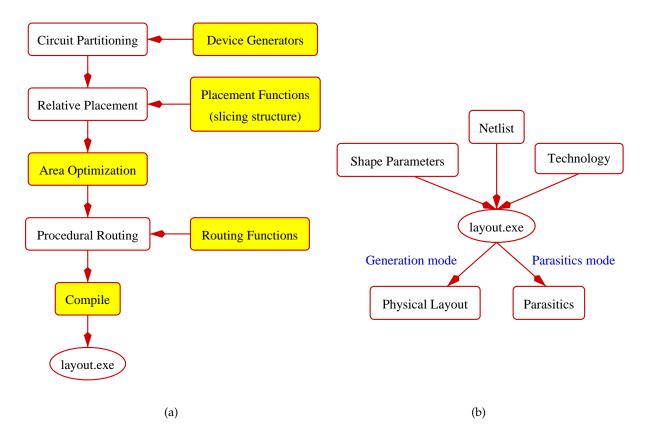

| 5.1  | CAIRO implementation                                                                  | 36 |

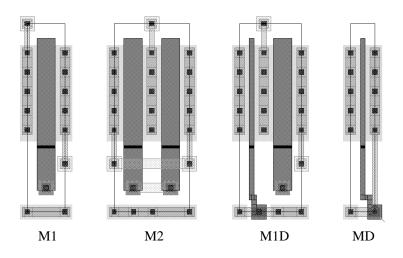

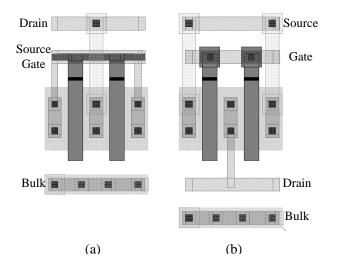

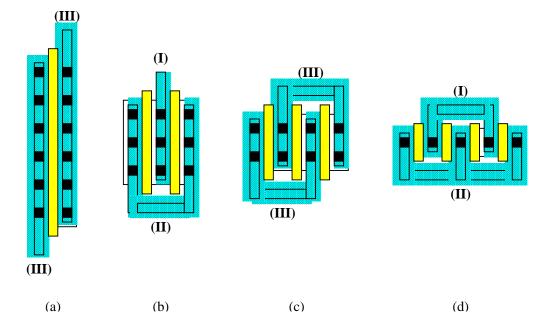

| 5.2  | Layout examples                                                                       | 38 |

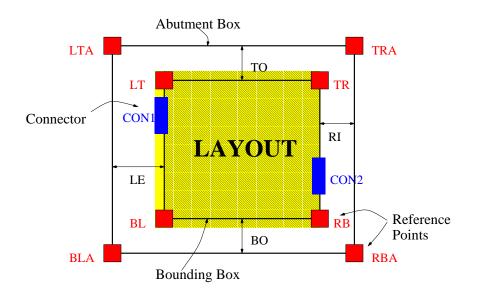

| 5.3  | Bloc Characteristics                                                                  | 39 |

| 5.4  | Motifs used in building transistors                                                   | 40 |

| 5.5  | Different transistor overlapping terminals                                            | 40 |

| 5.6  | Transistor folding                                                                    | 41 |

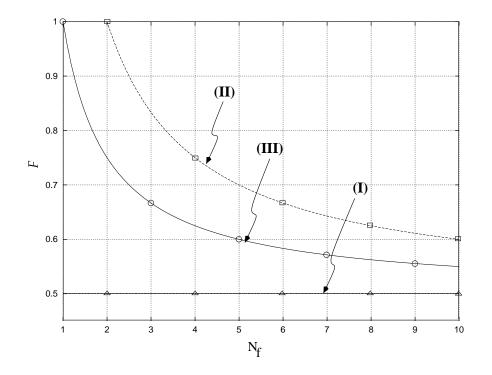

| 5.7  | Diffusion capacitance reduction factor                                                | 42 |

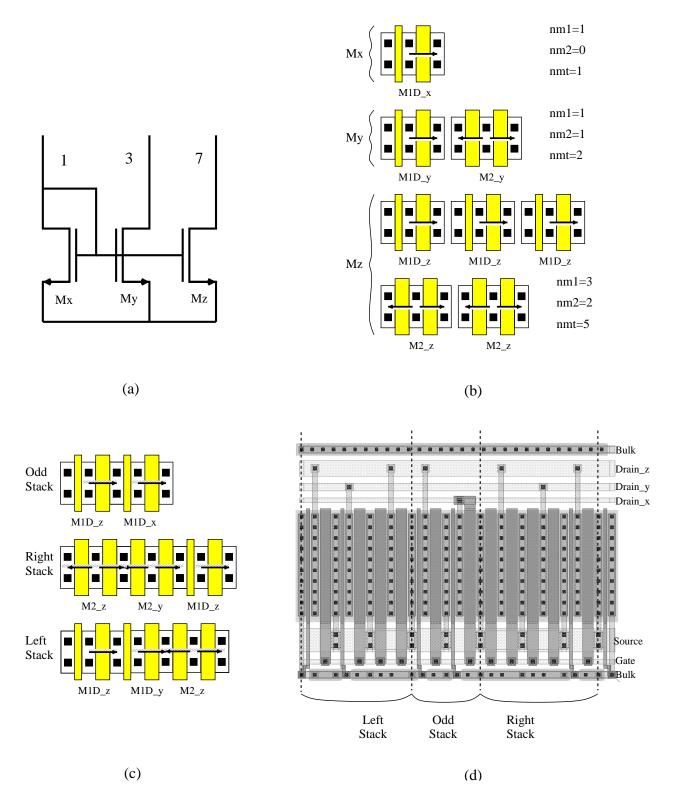

| 5.8  | Current mirror implementation                                                         | 44 |

| 5.9  | (a) CAIRO predefined hierarchy. (b) the corresponding slicing tree                    | 47 |

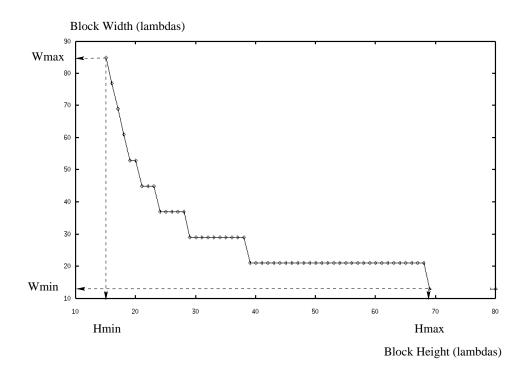

| 5.10 | Folded MOS transistor Shape function                                                  | 48 |

| 5.11 | Area optimization steps                                                               | 50 |

| 5.12 | Slice width optimization algorithm                                                    | 50 |

| 5.13 | Multilevel hierarchical optimization                                                  | 52 |

| 5.14 | A three-segment routing wire                                                          | 53 |

| 5.15 | Contact-Gate distance overhead due to symbolic layout                                 | 56 |

| 5.16 | Folded Cascode OTA                                                                    | 57 |

| 5.17 | Language description of the OTA circuit shown in Fig. 5.16                            | 58 |

| 5.18 | Folded Cascode OTA Layout in two different processes                                  | 60 |

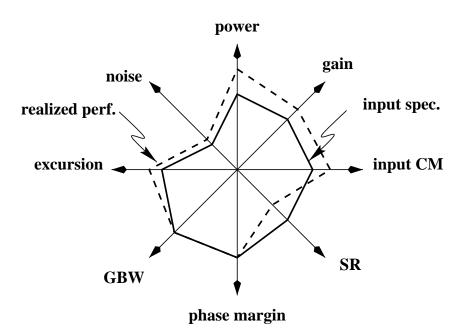

| 6.1  | Opamp design specification space                                                      | 64 |

| 6.2  | Differential pair                                                                     | 66 |

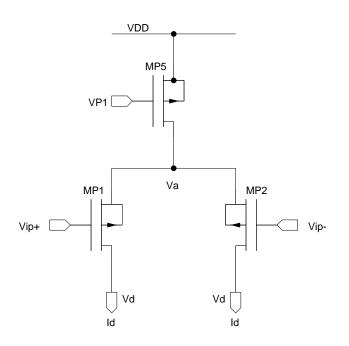

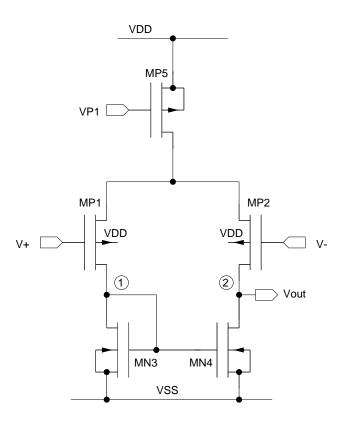

| 6.3  | Simple OTA                                                                            | 68 |

| 6.4  | OTA design procedure                                                                  | 70 |

### LIST OF FIGURES

| 6.5  | OTA window in COMDIAC                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------|

| 6.6  | OTA: (a) main parameters and (b) transistor bias                                                                  |

| 6.7  | OTA: (a) obtained results and (b) layout parasitics calculation and generation 73                                 |

| 6.8  | OTA: verification by simulation                                                                                   |

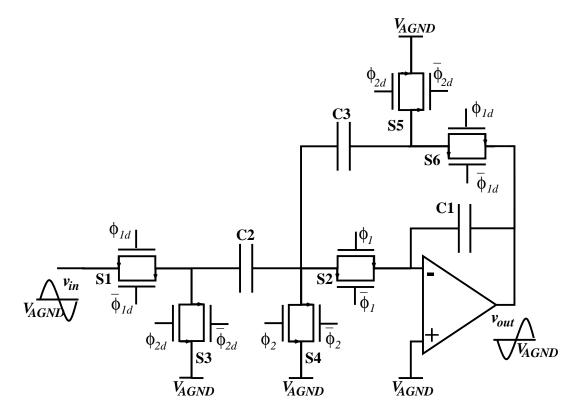

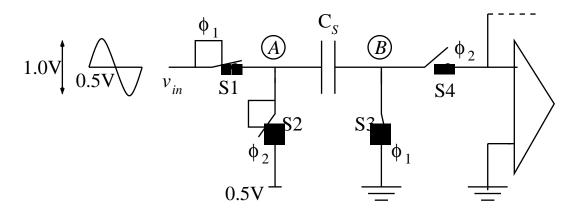

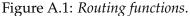

| 7.1  | A first-order Switched-capacitor low-pass section                                                                 |

| 7.2  | Basic switch bootstrapping circuit                                                                                |

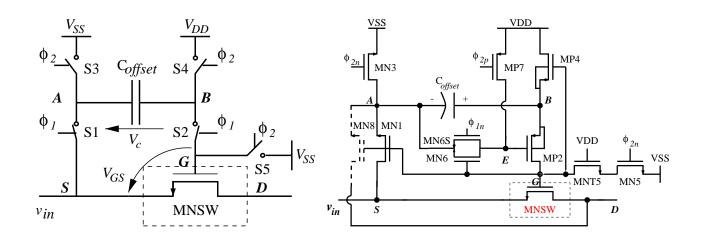

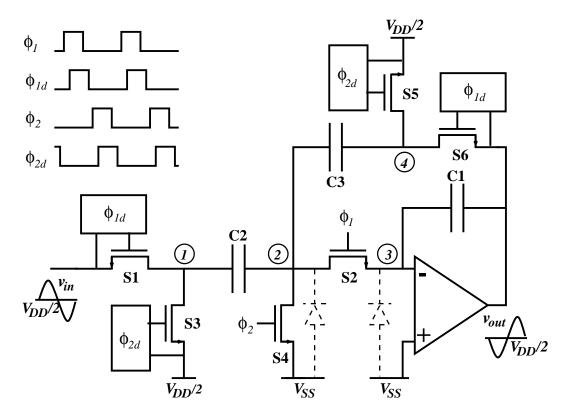

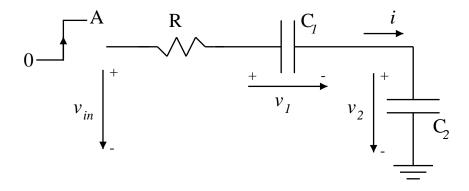

| 7.3  | The SC section shown in Fig. 7.1 using the charge cancellation scheme                                             |

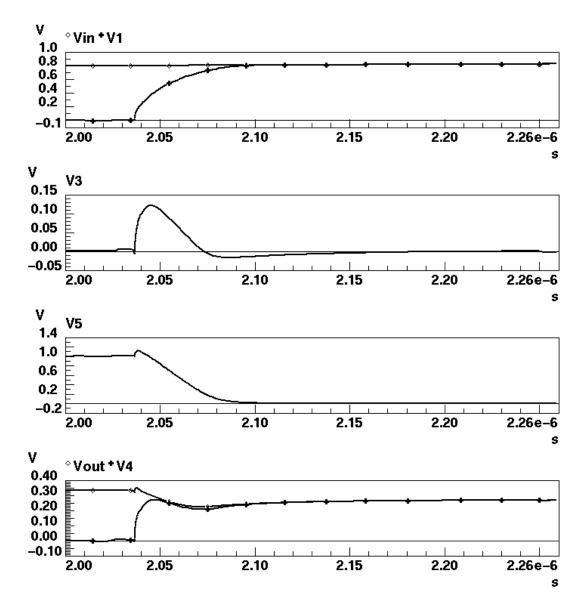

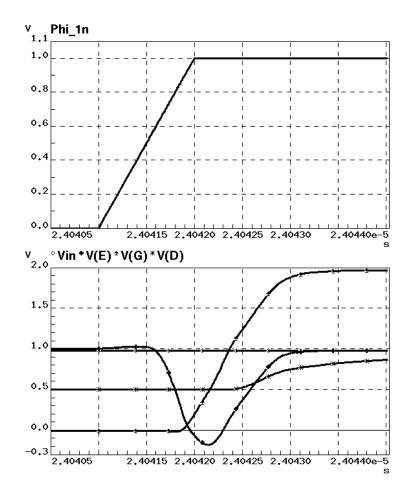

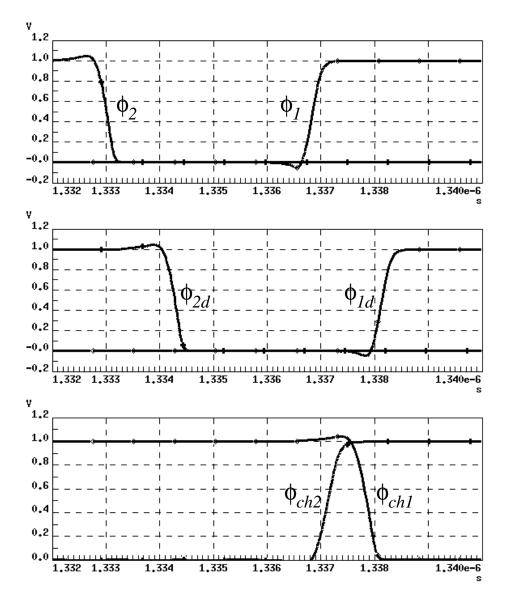

| 7.4  | Simulation of the integration phase $\phi_1$ transition of Fig. 7.3                                               |

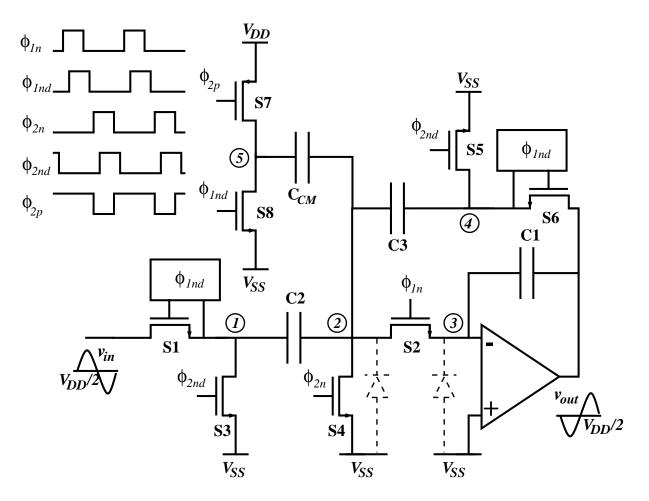

| 7.5  | The SC section shown in Fig. 7.1 using the double reference voltage technique $84$                                |

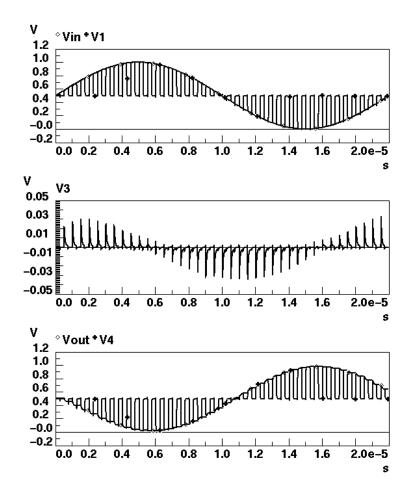

| 7.6  | Simulation of the low-pass SC section shown in Fig. 7.5                                                           |

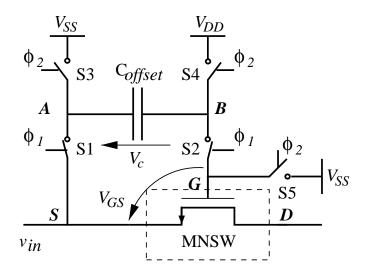

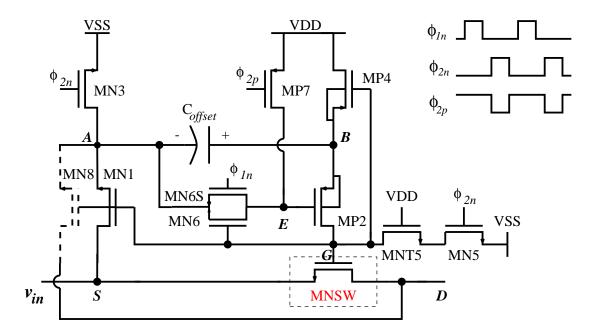

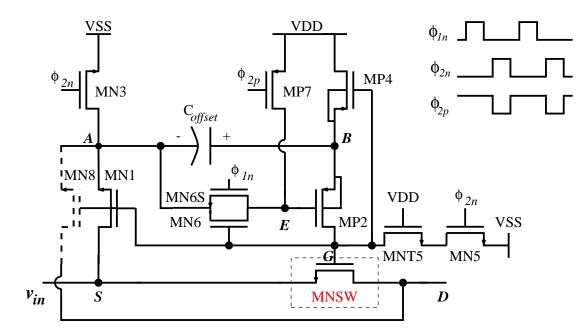

| 7.7  | Proposed implementation of the switch bootstrapping circuit                                                       |

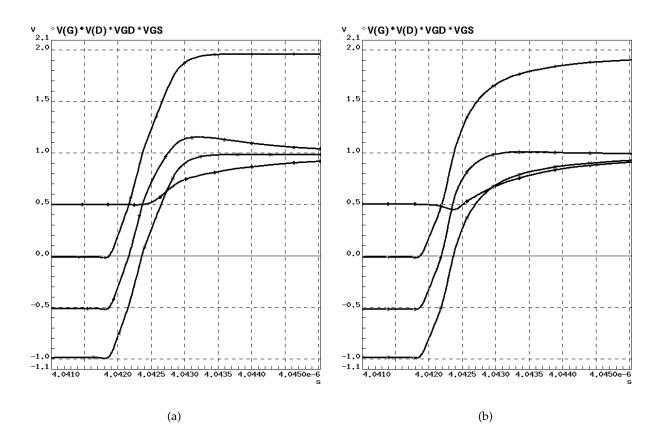

| 7.8  | Simulation of the turn on transition of the bootstrapped switch                                                   |

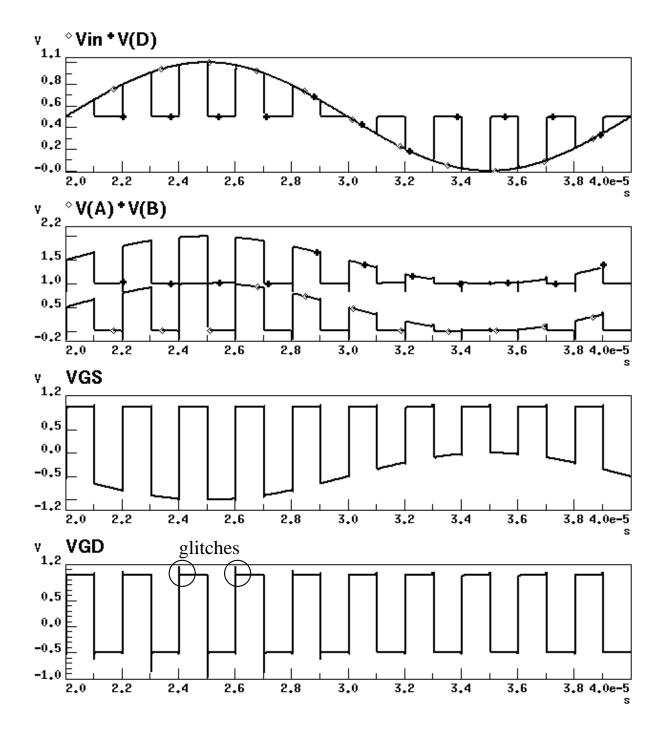

| 7.9  | Simulation of the bootstrapped switch S1 circuit operation in Fig. 7.5                                            |

| 7.10 | Gate-drain oxide transition overstress simulation                                                                 |

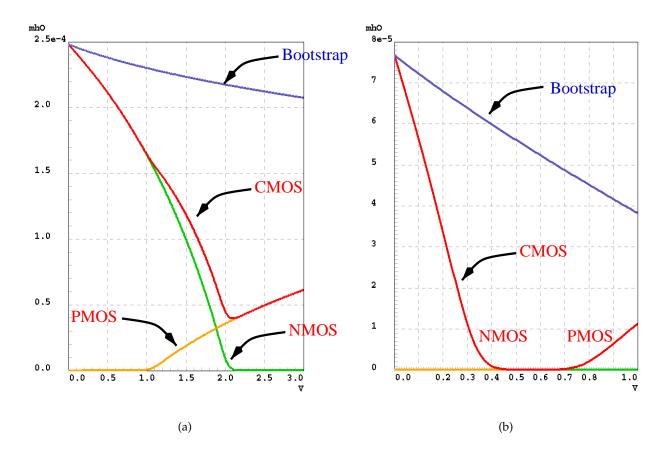

| 7.11 | Comparison of the bootstrapped and the CMOS switch conductance 90                                                 |

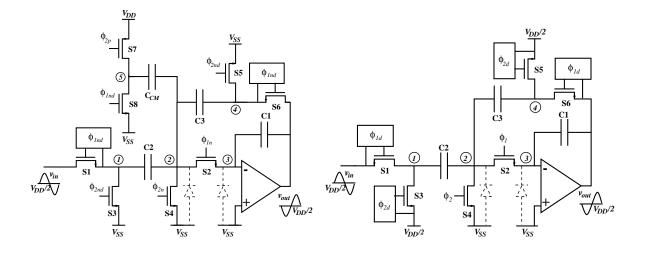

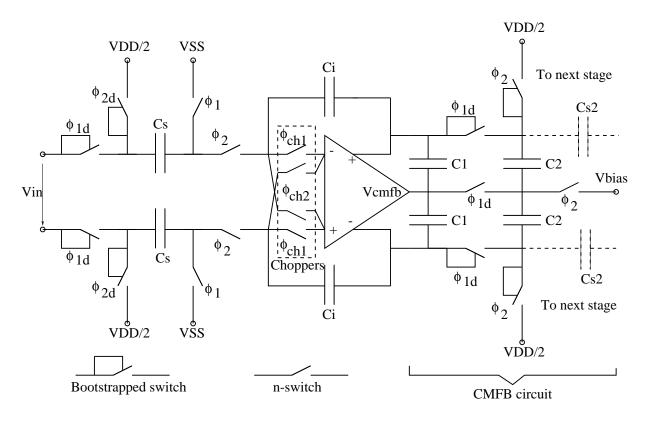

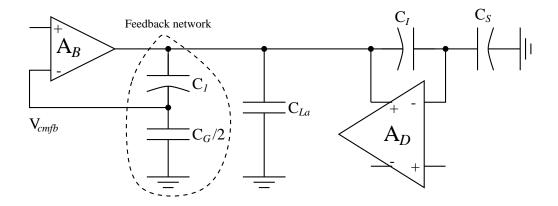

| 7.12 | Fully differential integrator using bootstrapped switches                                                         |

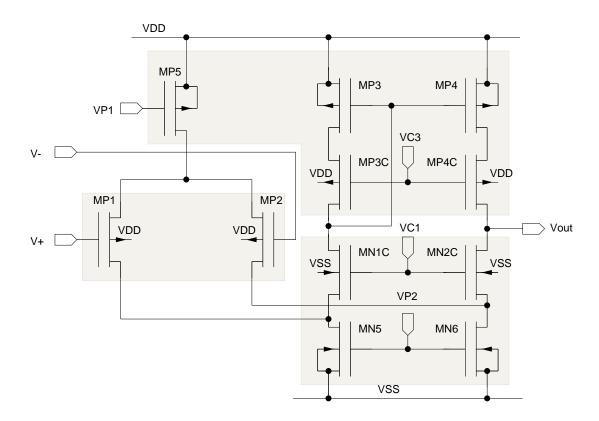

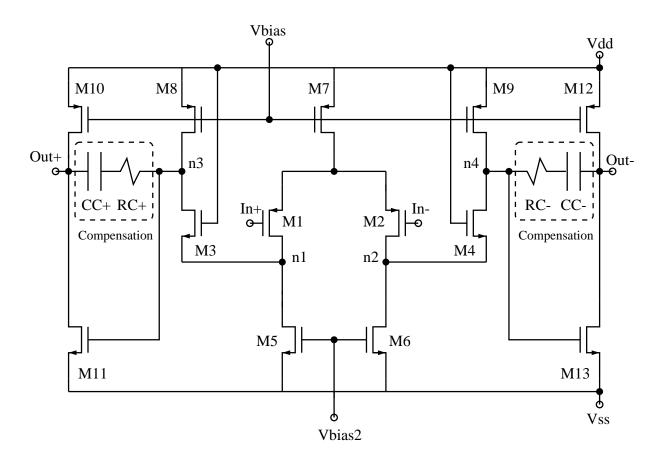

| 7.13 | Basic opamp structure with Miller compensation                                                                    |

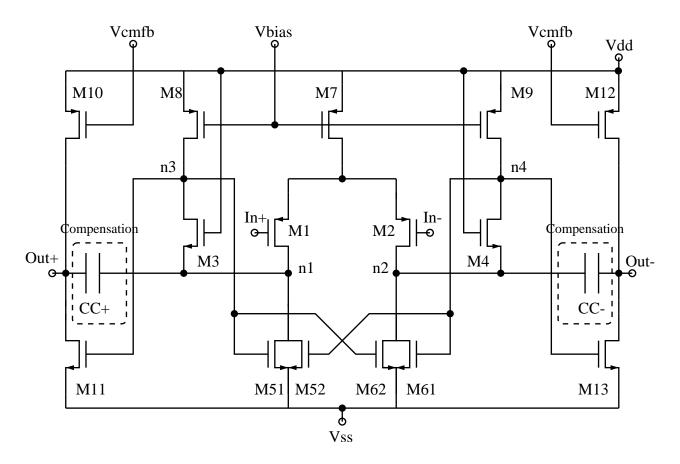

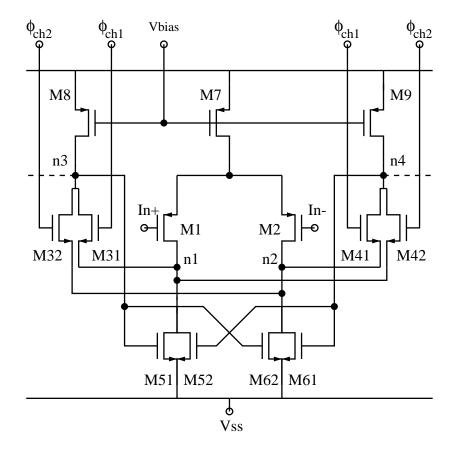

| 7.14 | Modified opamp schematic with cascode compensation                                                                |

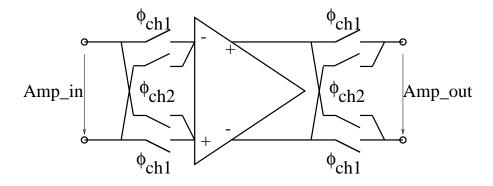

| 7.15 | Chopper stabilization, circuit implementation                                                                     |

| 7.16 | Output chopping using the cascode transistors                                                                     |

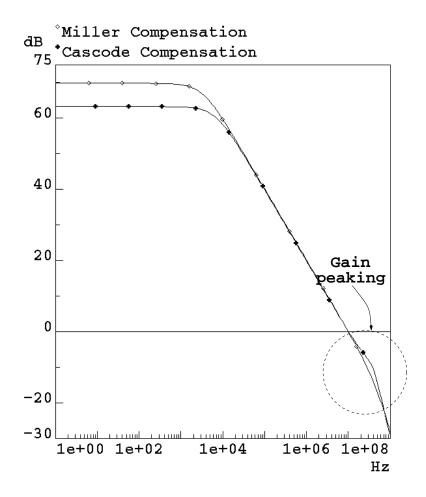

| 7.17 | Simulated Open-loop Gain for the two compensation schemes                                                         |

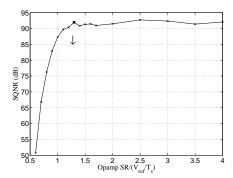

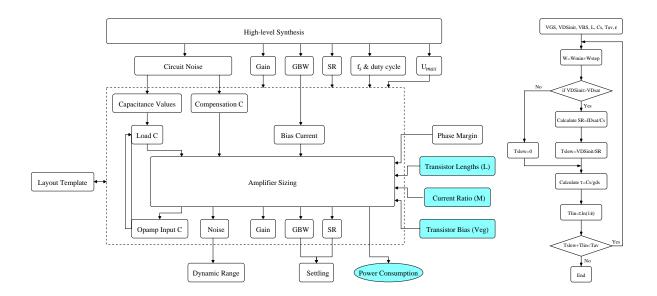

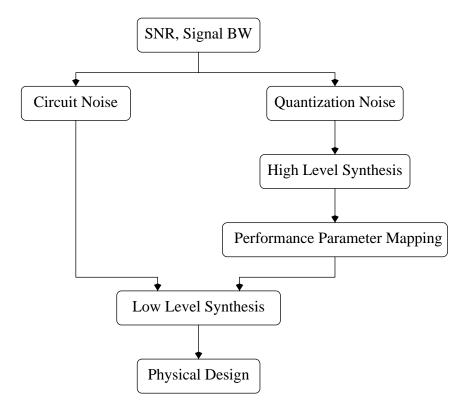

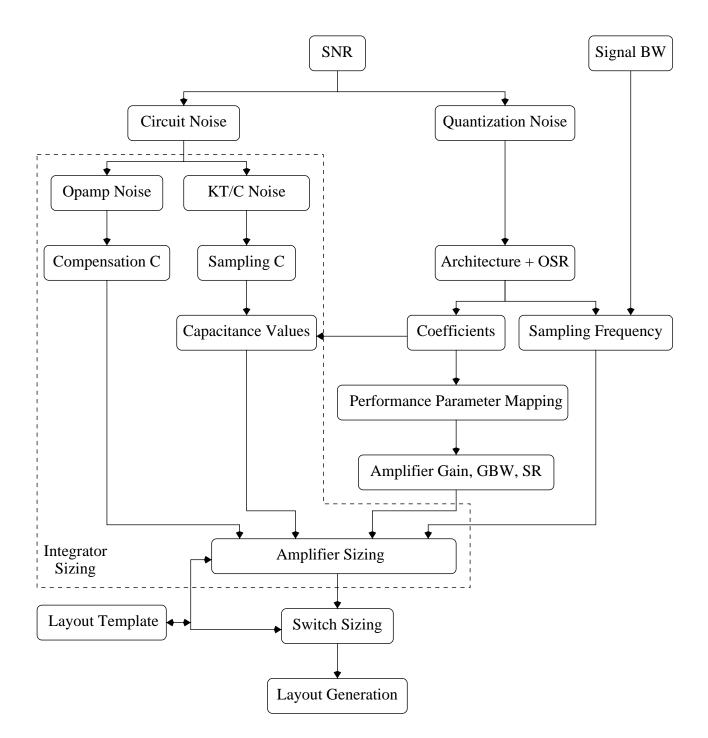

| 8.1  | Design flow                                                                                                       |

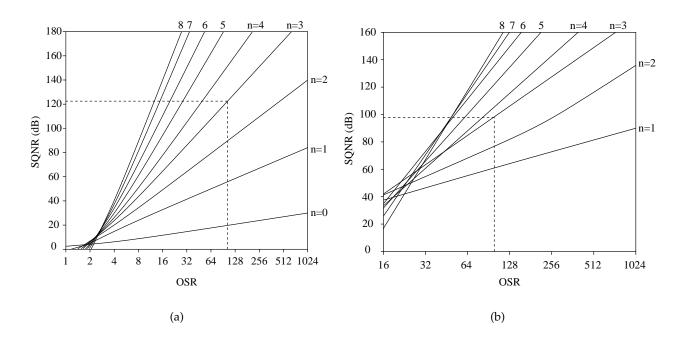

| 8.2  | Theoretical and maximum achievable SQNR                                                                           |

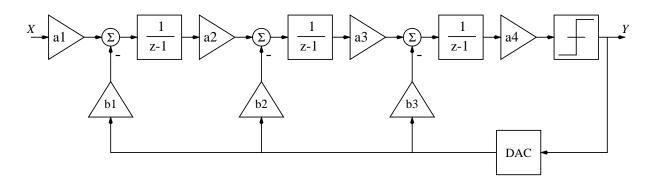

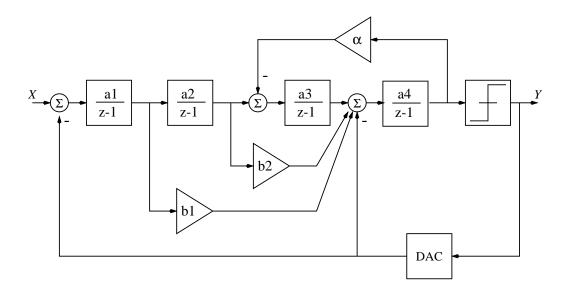

| 8.3  | Modulator topology                                                                                                |

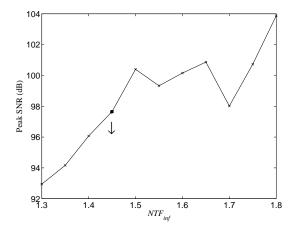

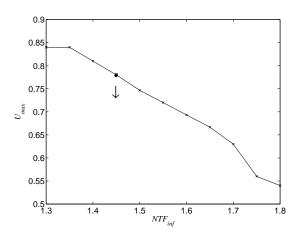

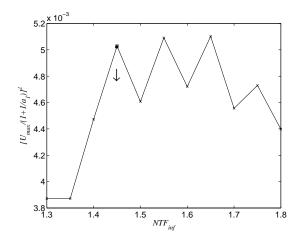

| 8.4  | Peak SQNR vs. the noise transfer function out-of-band gain                                                        |

| 8.5  | Maximum allowable input vs. the noise transfer function out-of-band gain 106                                      |

| 8.6  | $(U_{max}/(1+1/a_1))^2$ vs. the noise transfer function out-of-band gain $\ldots \ldots \ldots \ldots \ldots 106$ |

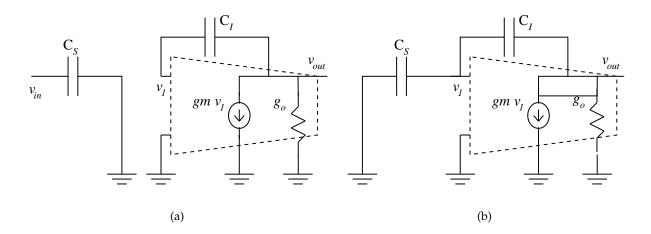

| 8.7  | SC integrator using a simple one-pole opamp model                                                                 |

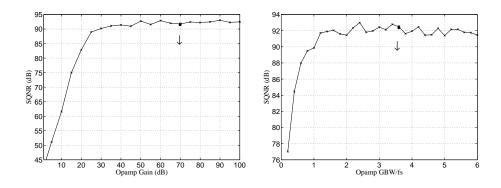

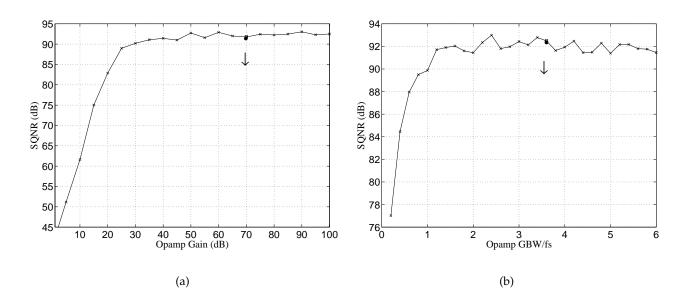

| 8.8  | SQNR vs. the amplifier gain and $GBW/f_s$                                                                         |

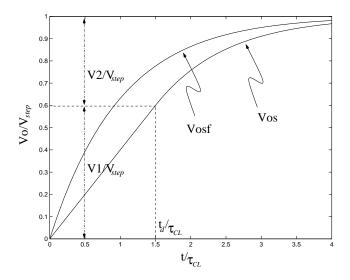

| 8.9  | Integrator slew-free output (Vosf) and slewing output (Vos)                                                       |

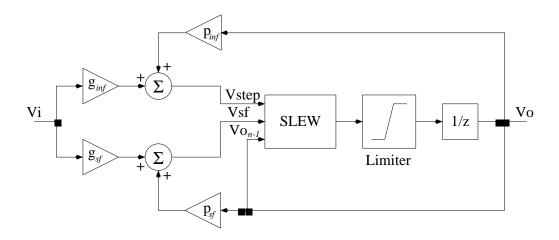

| 8.10 | Integrator model                                                                                                  |

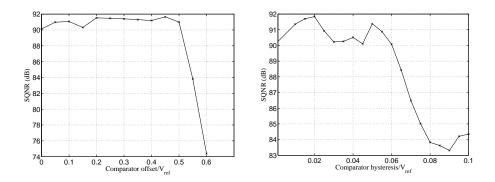

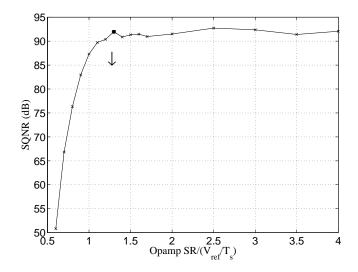

| 8.11 | SQNR vs. amplifier SR                                                                                             |

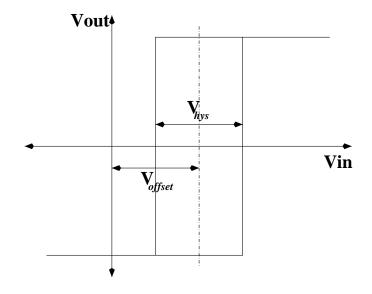

| 8.12 | Comparator offset and hysteresis                                                                                  |

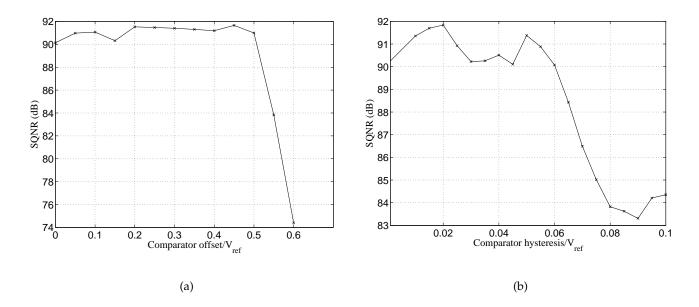

| 8.13 | SQNR vs. the comparator offset and hysteresis                                                                     |

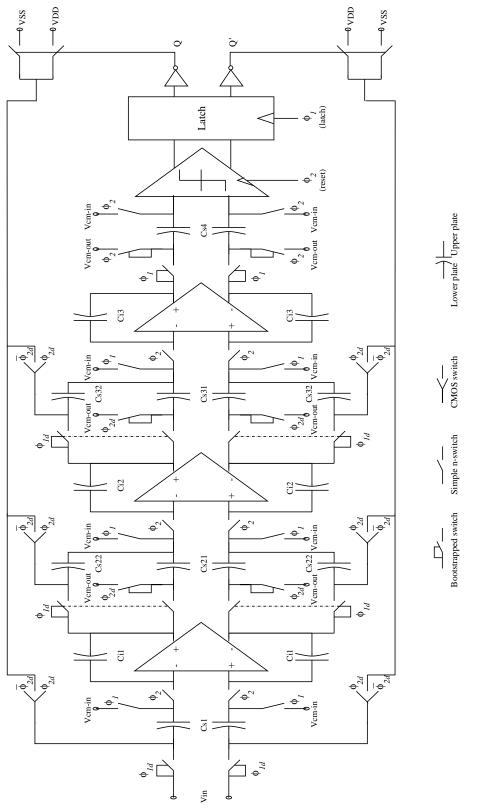

| 8.14 | Switched capacitor implementation of the modulator                                                                |

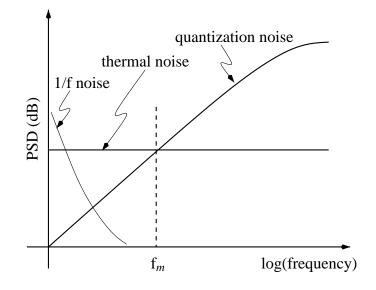

| 8.15 | Noise components                                                                                                  |

| 8.16 | Opamp schematic                                                                                                   |

#### LIST OF FIGURES

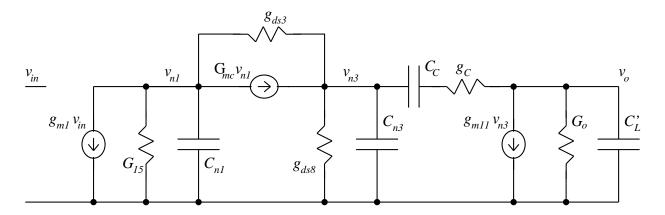

| 8.17 | Small signal model of the opamp shown in Fig. 8.16                    |

|------|-----------------------------------------------------------------------|

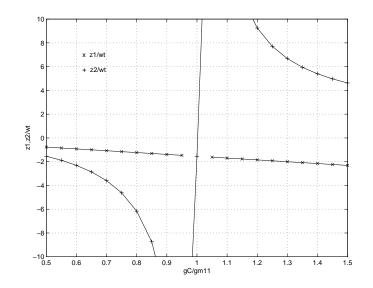

| 8.18 | Zeros plot                                                            |

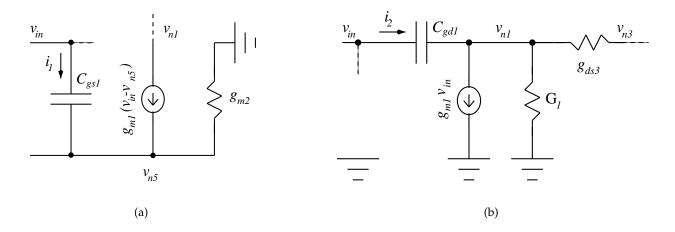

| 8.19 | Models for calculation of input currents: (a) $i_1$ and (b) $i_2$     |

| 8.20 | Worst-case settling time                                              |

| 8.21 | The common feedback closed-loop load                                  |

| 8.22 | Modulator design plan                                                 |

| 8.23 | Integrator design plan                                                |

| 8.24 | Sampling and integration phases in a low-voltage SC integrator        |

|      | Sampling/integration phases of Fig. 8.24                              |

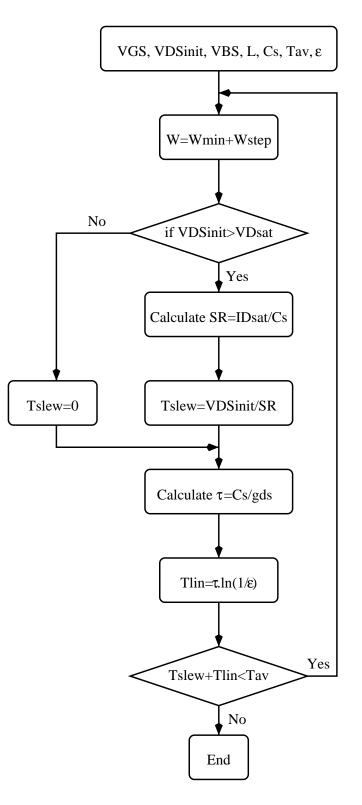

| 8.26 | Automatic switch sizing procedure                                     |

| 8.27 | Bootstrapped switch                                                   |

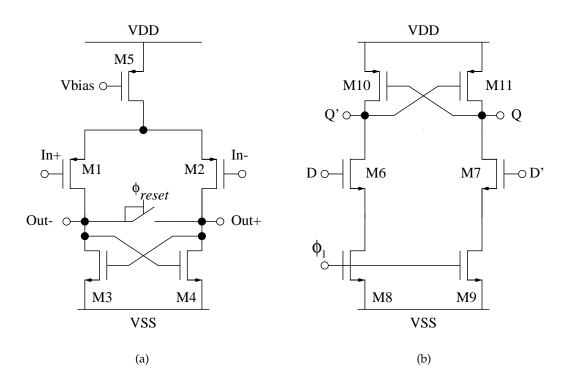

|      | Low voltage (a) comparator and (b) latch                              |

| 0.1  |                                                                       |

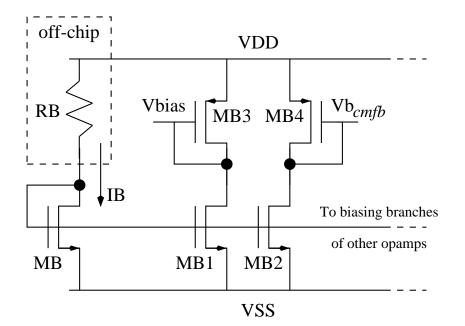

| 9.1  | Bias circuit for the first opamp                                      |

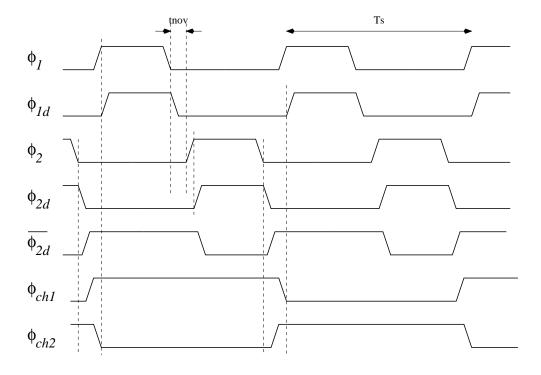

| 9.2  | Clock phases timing diagram                                           |

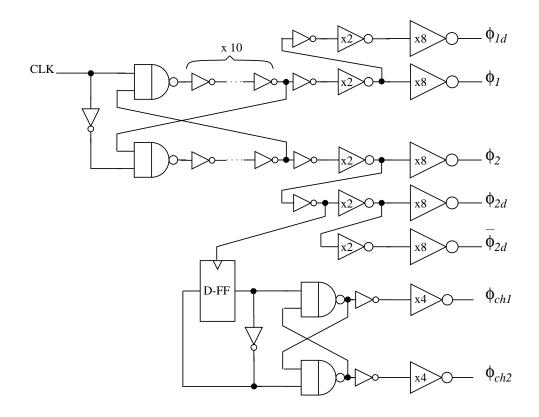

| 9.3  | Clock generator                                                       |

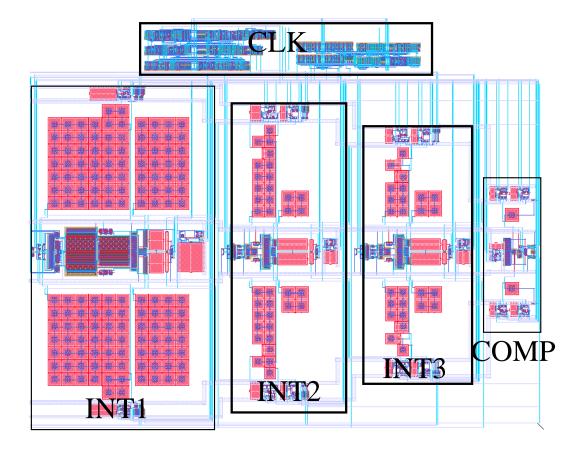

| 9.4  | Clock simulation results using worst-case transistor model            |

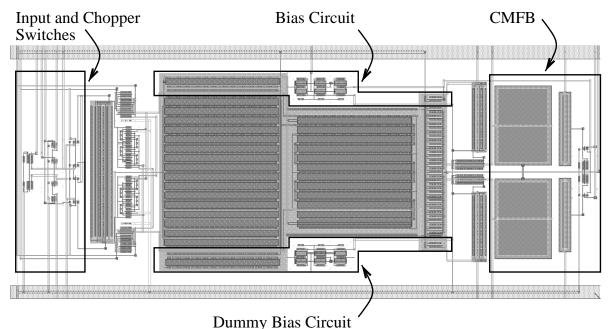

| 9.5  | Layout of the first stage amplifier                                   |

| 9.6  | Layout of the first integrator                                        |

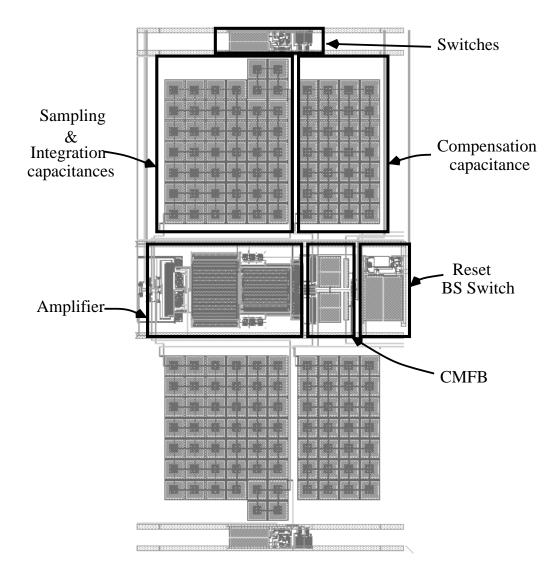

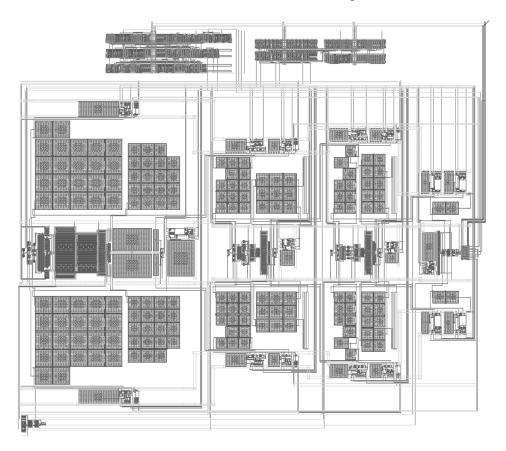

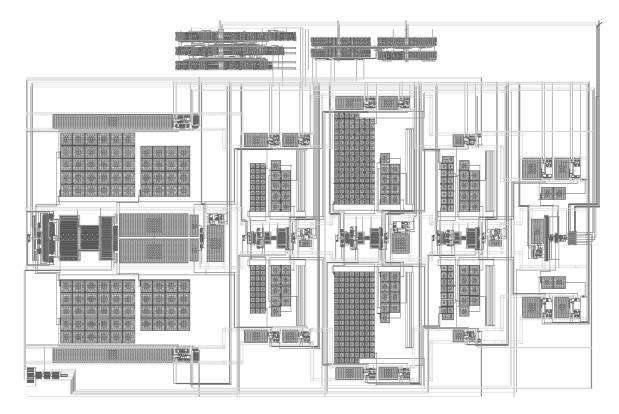

| 9.7  | Layout of the third-order modulator                                   |

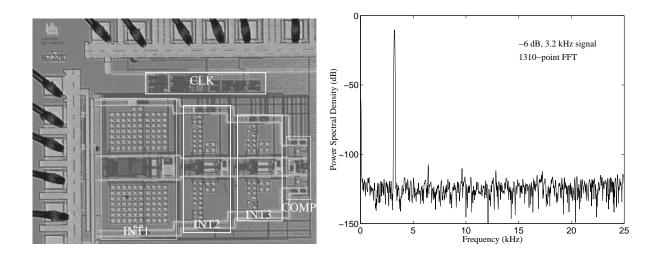

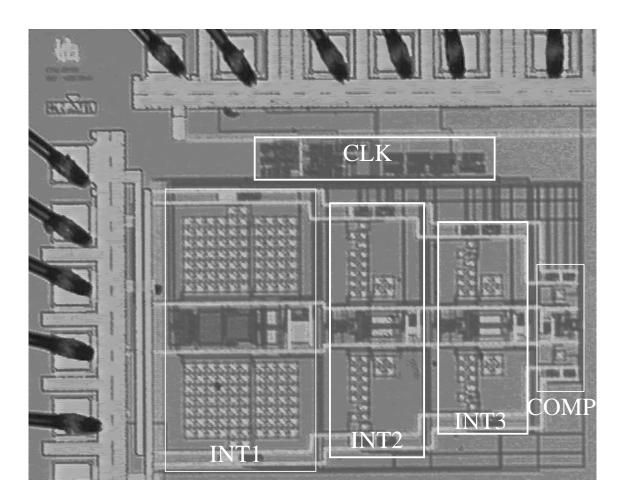

| 9.8  | Chip die photo                                                        |

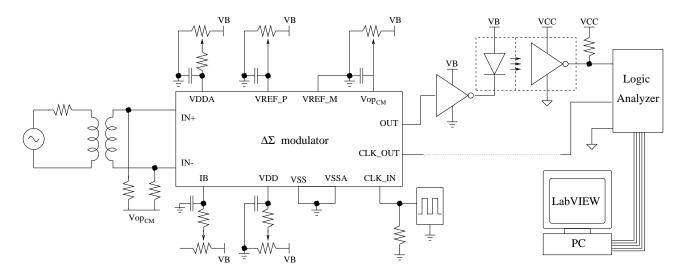

| 9.9  | Circuit diagram of the test setup. VB=1.5V and VCC=5V                 |

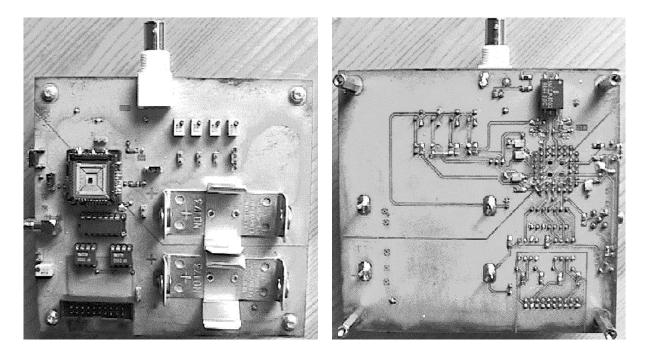

|      | PCB used for prototype test                                           |

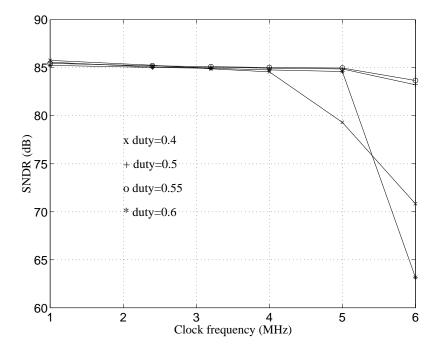

|      | SNDR versus clock frequency for different duty cycles                 |

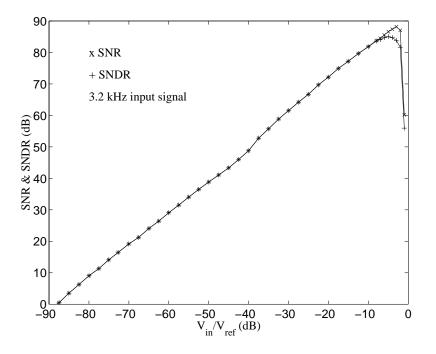

|      | Measured SNR & SNDR                                                   |

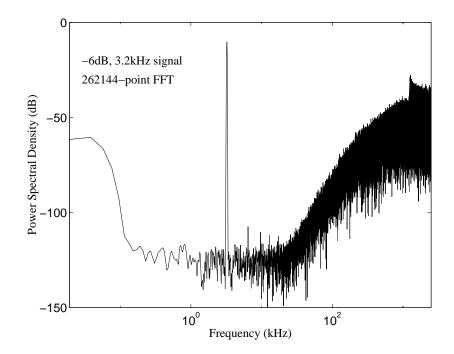

| 9.13 | Measured output spectrum                                              |

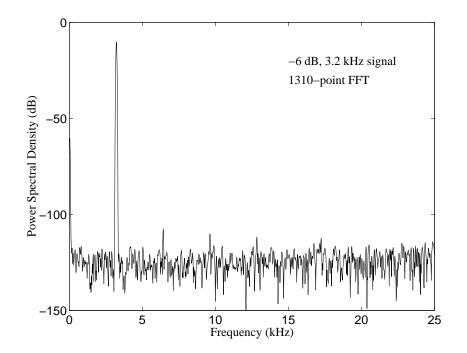

| 9.14 | Measured output baseband spectrum for a large amplitude signal        |

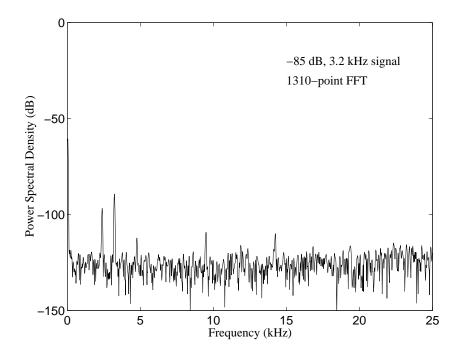

| 9.15 | Measured output baseband spectrum for a small amplitude signal        |

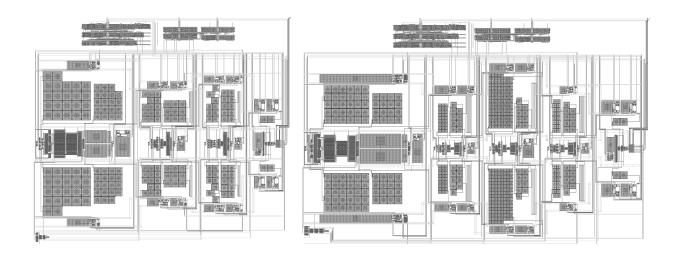

| 9.16 | Layout of the third-order modulator in another $0.35$ - $\mu$ process |

| 9.17 | Fourth-order modulator topology                                       |

| 9.18 | Layout of the fourth-order modulator in 0.35- $\mu$ process           |

| A.1  | Routing functions                                                     |

| B.1  | <i>R-C-C</i> network                                                  |

| B.2  | SC section using the charge cancellation scheme                       |

| B.3  |                                                                       |

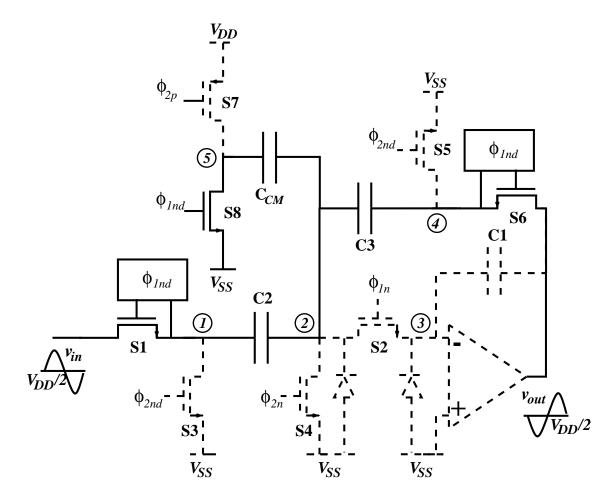

|      | SC branches connected to node 2 in Fig. B.2 during $\phi_1$           |

# List of Tables

| 3.1 | Comparison of cell sizing strategies 17                                               |

|-----|---------------------------------------------------------------------------------------|

| 4.1 | Transistor widths in $\mu$ m for two sizings of the OTA shown in Fig. 4.2             |

| 5.1 | CAIRO device generators                                                               |

| 5.2 | Transistor device generator parameters 46                                             |

| 6.1 | Sizing, layout and simulation results                                                 |

| 7.1 | Opamp sizes W/L in $\mu$ m for the cascode and Miller compensation schemes 98         |

| 7.2 | Opamp simulation results for the cascode and Miller compensation schemes 98           |

| 8.1 | Modulator Coefficients                                                                |

| 8.2 | Capacitor values (in pF), see section 8.5.2.3                                         |

| 8.3 | First integrator COMDIAC input parameters                                             |

| 8.4 | Opamp transistor bias and sizes for the first integrator                              |

| 8.5 | COMDIAC calculated modulator parameters                                               |

| 8.6 | Load capacitance and charging available time in the bootstrapping circuit 140         |

| 8.7 | Example of the bootstrapping circuit: input parameters                                |

| 8.8 | Example of the bootstrapping circuit: sizes                                           |

| 9.1 | Bias network gate-source voltages and sizes for the first integrator                  |

| 9.2 | Measured converter performance summary, refer to tables 8.3 and 8.5 for comparison157 |

| 9.3 | Measured circuits statistics                                                          |

| 9.4 | Performance comparison                                                                |

| 9.5 | Modulator in two technologies                                                         |

# Résumé Étendu en Français

Ce chapitre est un résumé étendu de la thèse. Chaque paragraphe de ce résumé correspond à un chapitre de la thèse.

### 1 Introduction

Comme les progrès technologiques permettent de créer des systèmes intégrés mixtes analogiquesnumériques, la complexité des circuits intégrés actuels continue à croître. Du fait que les systèmes intégrés deviennent plus complexes, la seule façon de concevoir des systèmes aussi denses est d'incorporer sur ces circuits des blocs existants, appelés aussi "Intellectual Property" (Propriété Intellectuelle), ou IP. Alors que ce concept obtient un certain succès dans la partie numérique des circuit mixtes, il est encore extrêmement difficile de réutiliser tel quel un bloc IP analogique.

Notre contribution porte sur trois points : Premièrement, nous proposons une méthode de conception pour la réutilisation de circuits analogiques, basée sur la co-conception électrique et physique du circuit. Deuxièmement, nous présentons des outils pour mettre en oeuvre cette méthode ; un outil de dessin des masques procédural, indépendant de la technologie, qui prend en compte les contraintes spécifiques des masques analogiques et un environnement dédié au dimensionnement de circuits, basée sur la réutilisation de savoir-faire. Enfin, l'application de cette méthode à l'aide de ces deux outils a été effectuée sur les circuits à capacités commutées fonctionnant sous très faible tension avec une faible consommation. Nous avons proposé de nouvelles architectures de circuits qui ont permis de concevoir et de réaliser un modulateur Delta-Sigma pour des application numériques audio, fonctionnant sous 1V et consommant 1mW. En dehors du fait que ce circuit est lui même intéressant, il démontre que la méthode que nous proposons, associée aux outils de CAO, sont particulièrement bien adaptés aux circuits mixtes à hautes performances.

#### 2 Problématique

Le chapitre 2 présente le contexte de la thèse en définissant le problème à résoudre et en introduisant les objectifs du travail.

#### 2.1 Les spécificités de la conception analogique

Les caractéristiques de la conception analogique, qui la différencient fortement de la conception numérique sont les suivantes :

- la hiérarchie est mal définie

- les performances sont définies par de nombreux paramètres

- le dimensionnement des composants élémentaires est critique pour la performance

- les composants d'un même circuit peuvent varier de plusieurs ordres de grandeur

- pour une même fonctionnalité, il existe une grande variété de topologies possibles

- la façon de dessiner les masques a une grande influence sur les performances

- les performances du circuit sont plus sensibles aux variations technologiques

- les différents niveaux de la hiérarchie du système intégré interagissent fortement

- les performances visées sont souvent aux limites de la technologie.

#### 2.2 Automatisation et réutilisation de la conception

Le but de la conception assistée par ordinateur est d'automatiser certaines tâches comme le dimensionnement, l'optimisation et la génération des masques [Gielen91]. Le but ultime est de rendre automatique tout le processus de conception depuis la description comportementale jusqu'au dessin des masques. Le degré d'automatisation est mesuré par le rapport entre le temps de conception d'un système réalisé de façon manuelle et celui utilisant les outils de synthèse [Ochotta98].

Par ailleurs le but de la réutilisation est de pouvoir réutiliser efficacement une réalisation existante pour un système dans un autre environnement et/ou un autre procédé de fabrication, tout en conservant à peu près les mêmes performances. Le concept de réutilisation ne se limite pas à reprendre exactement le même schéma électrique, car l'expertise accumulée peut être employée pour concevoir des circuits similaires à l'aide d'une approche bien définie et grâce à quelques cellules du premier circuit. Le degré de réutilisation est mesuré par la quantité d'informations et d'expériences qui sont transmises d'un circuit réussi aux réalisations suivantes.

Cependant, beaucoup de concepts et d'outils sont communs entre l'automatisation et la réutilisation de la conception.

#### 2.3 Modulateur Delta-Sigma très faible tension

Nous avons choisi les modulateurs Delta-Sigma fonctionnant sous très faible tension avec une faible consommation comme exemple de conception d'un bloc IP analogique, d'une part pour

#### Résumé Etendu

l'intérêt que présente leur conception et d'autre part car ils sont très adaptés pour tester l'approche que nous proposons ainsi que les outils de conception.

Les systèmes mono-puce à venir vont nécessiter l'intégration de parties purement numériques, de parties analogiques ainsi que de la mémoire, fonctionnant à faible tension. Le développement de techniques de conception adaptées à la faible tension et à la faible consommation sont ainsi requises pour deux raisons : D'une part, les progrès récents en téléphonie mobile et équipement portable ont accru les besoins en circuits mixtes faible-tension et basse-consommation. D'autre part, les progrès en procédés de fabrication CMOS sont déterminés par la vitesse de fonctionnement des systèmes numériques qui augmente grâce à la réduction continue des longueurs de grille. La diminution des longueurs de grille conduit à baisser les tensions d'alimentation pour éviter le claquage de grille.

Enfin, les convertisseurs analogiques-numériques sont des blocs indispensables comme interfaces des systèmes intégrés mixtes récents. Des techniques particulières comme la modulation Delta-Sigma permettent de réaliser des convertisseurs haute résolution, de vitesse moyenne, robustes, en technologie CMOS standard. Au contraire des circuits numériques, les circuits analogiques voient leur consommation augmenter quand la tension d'alimentation diminue [Sansen98]. Une estimation précise des éléments parasites est alors un bon moyen pour limiter la consommation de ces circuits.

#### 2.4 Objectifs du travail

Les objectifs de ce travail étaient ainsi définis :

- la définition d'une méthode compétitive de conception adaptée aux circuits analogiques réutilisables

- le développement de prototypes d'outils associés à la méthode. Il s'agit de :

- la création d'un outil dédié au dessin des masques CAIRO, indépendant de la technologie et permettant de prendre en compte les contraintes spécifiques de la conception analogique

- l'adaptation de l'environnement de dimensionnement COMDIAC, permettant la capture de l'expertise du concepteur

- la validation de la méthode et des outils associés par le biais de la conception d'un bloc IP analogique avec des performances exigeantes. Nous avons choisi les modulateurs Delta-Sigma très faible tension comme démonstrateur de notre méthode, dans une réalisation en capacités commutées, pour plusieurs technologies cibles.

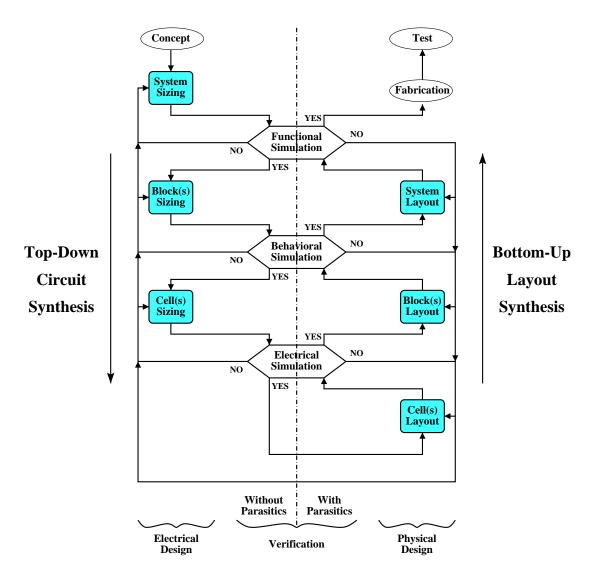

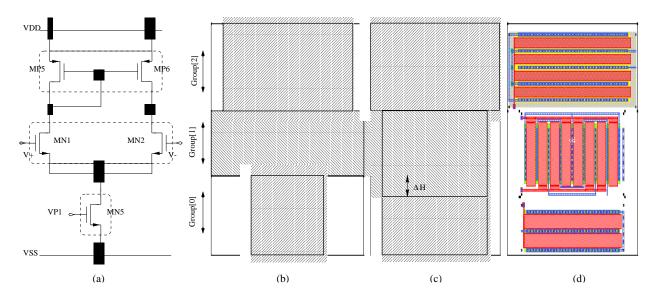

Figure 1: Étapes principales de la conception mixte.

## 3 Etat de l'Art

La figure 1 présente les étapes principales de la conception mixte :

- Dimensionnement du système : Pendant cette phase on choisit l'architecture du système complet. Le système est ensuite décomposé en une interconnexion hiérarchique de blocs fonctionnels dont les spécifications résultent de celles du système complet. L'automatisation de cette phase n'est possible que pour les systèmes dont l'architecture est fixée. L'exemple d'un système de pilote de vidéo est donné dans [Chang97], un autre [Donnay97] présente la synthèse, suivant trois méthodes différentes, d'un système d'acquisition analogique.

- Dimensionnement des blocs : Les blocs sont définis en tant que fonction indépendante avec une interface robuste qui permet de distinguer clairement le bloc de son environnement.

Il s'agit de boucles à verrouillage de phase, de convertisseurs analogiques-numériques ou de convertisseurs numériques- analogiques. Des outils de CAO ont été développés pour accélérer la conception de tels systèmes. Le cas d'un outil dédié à un convertisseur analogique-numérique cyclique est traité dans [Jusuf90], celui de la synthèse d'un convertisseur numérique-analogique en courant commutés CMOS dans [Neff95], et un ensemble d'outils dédiés aux modulateurs Delta-Sigma est présenté dans [Medeiro95] [Medeiro99].

- Dimensionnement des cellules : Les cellules sont définies comme des fonctions de base, de complexité réduite, utilisées pour construire un bloc, comme les amplificateurs et les oscillateurs. Dans cette phase, il s'agit de déterminer les tailles des composants élémentaires (transistor, capacité, résistance) du circuit associé à chaque cellule de manière à atteindre les performances requises pour le bloc. Les méthodes de dimensionnement sont classées en deux catégories : celles utilisant le savoir-faire esixtant, et celles utilisant l'optimisation.

- Les masques au niveau des cellules : Il s'agit ici de générer les masques des cellules à partir de la netlist dimensionnée et d'informations additionnelles sur les éléments parasites, l'appariement et les performances attendues. Les approches existantes peuvent aussi être classées suivant deux catégories : l'une basée sur l'utilisation du savoir-faire, ne pouvant être appliquée qu'à des topologies de circuit fixées, et l'autre, plus générale, basée sur l'optimisation. Dans la première catégorie on trouve que le savoir-faire peut être stocké sous une forme procédurale [Owen95] ou à travers l'utilisation de bibliothèques de topologies [Koh90], ou à l'aide de gabarits [Conway92] ou à travers une série de règles explicites [Bexten93]. Dans la seconde catégorie on trouve des approches qui réalisent le placement à l'aide d'algorithmes d'optimisation, suivi par la phase de routage [Rijmenants89], [Cohn91], [Lampaert95].

- Les masques au niveau des blocs : Quelques outils dédiés à des applications bien définies ont été développés pour automatiser la génération des masques [Jusuf90], [Neff95].

- Les masques au niveau du système : Les masques du système complet sont obtenus par placement et routage des différents blocs qui composent le système.

#### 3.1 Le contrôle des éléments parasites

Deux approches ont été utilisées pour contrôler automatiquement les éléments parasites :

La classification des signaux : Dans [Rijmenants89], on trouve que les signaux sont classés suivant leur caractère plus ou moins critique, de manière à minimiser les parasites sur les signaux sensibles et le couplage entre signaux bruités pendant le routage. Dans [Cohn91], le placement et le routage reposent sur la minimisation des divers éléments parasites pondérés ainsi que sur le respect des contraintes d'appariement intégrés dans une fonction de coût. Cependant, aucune stratégie claire n'est proposée pour fixer les différents poids de la fonction de coût qui doivent être fixés par le concepteur en fonction de son expérience.

2. L'optimisation sous contrainte : Plus récemment, des outils de génération des masques basés sur la définition de contraintes et utilisant une analyse de sensibilité des performances du circuit [Choudhury90b], [Charbon93] ont été proposés pour le placement [Charbon92] et le routage [Choudhury90a]. La méthode de [Lampaert95] a éliminé la phase intermédiaire d'élaboration de contraintes physiques en optimisant le dessin des masques directement à partir des contraintes sur les performances électriques du circuit. Cependant, le temps CPU requis pour satisfaire les contraintes est toujours grand, ce qui limite l'utilisation de cette méthode à des circuits à faible nombre de composants.

#### 3.2 Propriété intellectuelle analogique et migration technologique

Un des problèmes majeurs qui se pose lorsque l'on souhaite réutiliser un circuit analogique est celui de la migration technologique. On doit toujours passer par une étape de redimensionnement avant de pouvoir porter un circuit analogique d'une technologie à une autre. Une solution est d'utiliser des outils de dimensionnement des cellules. Cependant, du fait qu'il existe une forte interaction entre les différents niveaux hiérarchiques d'un circuit analogique, on est souvent obligé d'effectuer des modifications au niveau des blocs et des compromis au niveau des cellules. La plupart des outils de dimensionnement ne permettent pas l'interaction du concepteur. Une autre approche consiste à développer des outils de synthèse dédiés à une application particulière [Jusuf90] [Neff95] [Medeiro95]. Le développement de générateurs spécifiques nécessite un effort considérable, demande du temps et représente un travail de préparation et de suivi qui suppose que le concepteur du générateur ait acquis une parfaite compréhension du fonctionnement du circuit et puisse améliorer le générateur au fur et à mesure de son expérience. Un des inconvénients de cette approche est qu'un générateur ne prend en compte qu'un certain nombre de paramètres, bornés, en fonction de l'architecture du circuit ce qui limite l'espace des solutions. Plus récemment des expériences pour réutiliser un circuit existant ont été menées en utilisant un raisonnement qualitatif [Francken99] ou un système à base d'optimisation [Phelps00]. Dans les deux cas la plupart des intentions du concepteur original sont perdues dans les réalisations ultérieures.

#### 4 Méthode de conception orientée dessin des masques

Chaque fois que l'on cherche à utiliser à nouveau un bloc analogique existant dans un contexte différent, que ce soit un système différent qui nécessite une modification des performances, ou le même système dans une autre technologie, on doit toujours modifier les tailles des composants

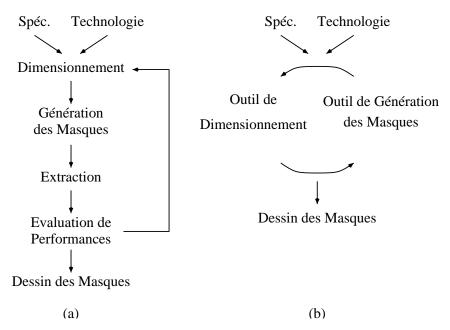

Figure 2: Méthodologie de compensation des éléments parasites: (a) traditionelle et (b) proposée.

du circuit. Vu la quantité de paramètres qu'il est souhaitable de conserver d'une réalisation à une autre, la façon la plus efficace de concevoir des blocs réutilisables est d'inclure l'information adéquate, concernant aussi bien la synthèse que les masques, lors de la conception du premier circuit.

Ce travail propose une méthode de conception analogique pour la réutilisation, basée sur des plans de conception. Un plan global de conception est constitué par une succession d'étapes qui comprennent d'une part des équations analytiques et des modèles fonctionnels/comportementaux pour la synthèse au niveau système, accompagnés d'une méthode permettant d'en déduire les paramètres des blocs dans les niveaux hiérarchiques inférieurs. D'autre part, pour ce qui concerne la synthèse bas niveau et la génération des masques, la conception s'appuie sur des outils de CAO basés sur la définition de gabarits. Par ailleurs, la conception d'un circuit repose sur une forte interaction entre les phases de dimensionnement et de génération des masques afin d'accélérer le cycle de conception, d'en améliorer la qualité et de faciliter la migration dans une autre technologie.

On résout souvent le problème de compensation des éléments parasites résultant du dessin des masques par un processus itératif montré sur le flot de conception de la figure 2(a). Une conception traditionnelle met en oeuvre une suite laborieuse de boucles enchaînant le dimensionnement du circuit, puis la génération des masques, l'extraction de la netlist avec les éléments parasites et l'évaluation des performances du circuit en prenant en compte ces parasites.

Dans ce travail, le dimensionnement et la génération des masques ne sont plus considérés comme deux phases distinctes (voir figure 2(b)). Cette approche est une extension de celle qui a été proposée dans [Onodera90]. Pendant le dimensionnement, l'outil de dessin des masques est

utilisé pour calculer les éléments parasites résultant d'une certaine réalisation physique. Cet outil doit être d'une part rapide car il est susceptible d'être appelé plusieurs fois lors du dimensionnement d'un circuit. D'autre part, les solutions de placement obtenues à chaque itération, doivent être proches de manière à aider la convergence des éléments parasites. Ces considérations nous ont conduits à utiliser une approche basée sur la capture du savoir-faire, qui repose sur le concept de gabarits ainsi définis :

- le gabarit éléctrique : il définit une topologie de circuit sans aucune information sur les tailles des composants,

- le gabarit physique : il définit à la fois le placement relatif des éléments et leur routage pour une topologie de circuit fixée, sans aucune information sur la tailles des composants ou le facteur de forme final de circuit.

Un premier dimensionnement est réalisé d'après les spécifications sur les performances, en supposant qu'aucun transistor n'est replié. Après cette phase d'initialisation, les informations quantitatives suivantes sont transmise à l'outil de dessin des masques :

- les tailles des transistors (L et W),

- les courants de drain et de source des transistors,

- des précisions sur la réalisation physique de certains composants (appariement, ...),

- un paramètre physique global définissant le facteur de forme du circuit total.

Muni de ces données ainsi que du gabarit physique du circuit, l'outil de dessin des masques est exécuté dans un mode particulier appelé *mode de calcul des parasites*. Dans ce mode, il n'y a pas de réelle génération de masques, l'outil calcule seulement les éléments parasites et transmet en retour à l'outil de dimensionnement :

- le style du transistor physique (i.e. le nombre de repliements, la surface de diffusion, ...),

- les capacités parasites de routage, y compris les capacités de couplage,

- la surface exacte des caissons pour permettre le calcul des capacités de caissons flottants.

Ce procédé est itéré jusqu'à obtenir la convergence des parasites. L'outil de dessin des masques est alors exécuté dans un mode appelé *génération* où les masques sont réellement créés d'après le gabarit physique.

En comparant les figures 2(a) et (b), on remarque que les itérations visant à compenser les parasites existent toujours. Cependant, la grande différence est que cette boucle de compensation a été automatisée grâce au mode *calcul des parasites* de l'outil de masques, ce qui offre les avantages suivants :

- On peut comparer diverses réalisations physiques des mêmes composants,

- On ne peut pas séparer le comportement des composants de leurs réalisations physiques, ce qui est particulièrement important dans le cas des inductances intégrées.

- On peut optimiser certaines caractéristiques du circuit en exploitant la possibilité de minimiser les capacités parasites.

- On peut prendre en compte certaines contraintes physiques lors du dimensionnement.

- On raccourcit le temps de conception total en supprimant les itérations manuelles laborieuses dimensionnement-masques-extraction-simulation.

- On garantit que le circuit réalisé atteint les spécifications attendues car on a tenu compte des éléments parasites.

Bien que nous ayons remarqué que les niveaux hiérarchiques d'un circuit analogique soient mal définis, l'utilisation de la hiérarchie reste un des moyens les plus efficaces pour gérer la complexité d'un circuit. Il faut noter que les dégradations de performances dues aux parasites peuvent provenir de plusieurs niveaux hiérarchiques. Par ailleurs, afin d'obtenir un circuit final rectangulaire, ce qui préférable pour faciliter le plan de masse au niveau système, il faut contrôler la forme des blocs en fonction de la forme du circuit total, puis la forme des composants plus élémentaires en fonction de la forme des blocs. C'est pourquoi nous avons choisi l'approche descendante aussi bien pour la synthèse que pour le dessin des masques, dans cette approche orientée réalisation physique. Générer les masques d'un circuit suivant une approche descendante suppose que l'optimisation globale de surface puisse jouer sur la forme des cellules dans les différents niveaux hiérarchique grâce à une propagation descendante des contraintes.

# 5 Dessin procédural des masques avec calcul des parasites

Afin de pouvoir être conforme à notre approche, l'outil de génération des masques doit satisfaire les conditions suivantes :

- Il doit comporter une méthode précise de calcul des parasites.

- Il doit permettre de respecter les contraintes des masques analogiques.

- Il doit permettre différentes réalisations physiques d'un même composant.

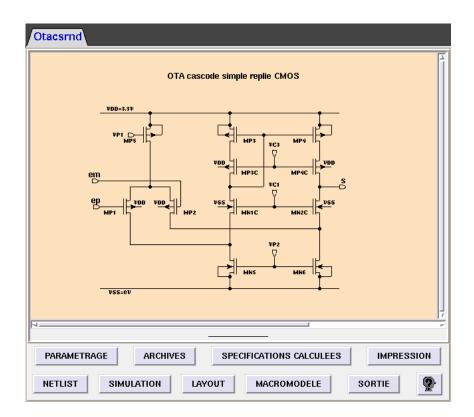

L'outil de dessin des masques se présente sous la forme d'un langage, appelé CAIRO, composé d'un ensemble de fonctions écrites en langage C. Ce langage constitue un sur-ensemble de Genlib, ensemble de primitives physiques [Pétrot94].

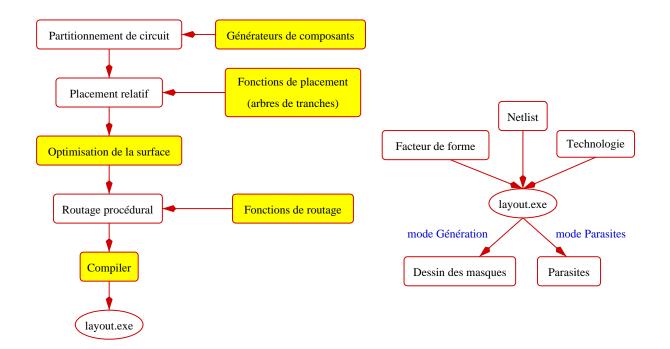

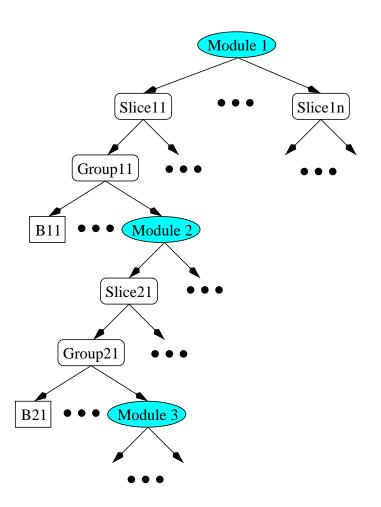

Les rectangles grisés de la figure 3(a) montrent les différents ressources du langage, il s'agit de :

Figure 3: Langage CAIRO: (a) La description du savoir-faire (b) Génération des masques et calcul des parasites.

- des générateurs optimisés de composants simples,

- des fonctions de placement relatif,

- un algorithme original d'optimisation de la surface,

- des fonctions de routage relatif,

- un script de compilation basé sur le compilateur du langage C.

La description des masques du circuit, réalisée avec les fonctions de CAIRO, est compilée puis liée avec la bibliothèque de CAIRO. Le programme exécutable permet de prendre en entrée une netlist dimensionnée, une contrainte sur la taille du circuit total et un fichier de paramètres technologiques. Il peut délivrer en sortie soit les éléments parasites associés à la netlist, soit le dessin des masques physiques, voir figure 3(b). Il faut souligner le fait que la description des masques est indépendante des tailles des composants et de la technologie.

# 5.1 Les contraintes des masques analogiques

S'il est indispensable que l'outil CAIRO soit rapide, il est aussi capital qu'il puisse satisfaire les contraintes analogiques. Il s'agit de :

- Contraintes sur les éléments parasites : Tous les transistors sont construits à partir d'un motif élémentaire qui permet de déterminer la position, la largeur, et la nature des connecteurs et des fils de connexion. Ceci fournit un degré de liberté supplémentaire pour contrôler le couplage entre signaux à l'intérieur même d'un transistor en fonction des applications [Wolf99]. Les transistors dont la grille est très large peuvent être générés sur plusieurs empilements. Le repliement des transistors diminue les capacités parasites de diffusion par rapport au substrat. On peut ainsi minimiser la capacité parasite d'un signal en jouant sur le nombre de repliements connectés sur ce signal. Ce contrôle des éléments parasites permet d'améliorer les caractéristiques fréquentielles d'une réalisation physique.

- Contraintes d'appariement : Les miroirs de courant constituent un des cas où l'appariement entre les transistors est déterminant. Nous avons développé un algorithme dédié au dessin des masques de miroirs de courant. Cet algorithme prend en compte le sens du courant dans la grille et garantit le maximum d'entrecroisements entre transistors centrés, autour du centre de l'empilement.

- Contraintes de fiabilité : Elles sont essentielles pour le fonctionnement du circuit à long terme. Ainsi les largeurs des fils dans chaque composant, des fils de routage et le nombre de contacts sont calculés d'après le courant de polarisation qui les traverse, de manière à respecter la densité de courant maximale permise par la technologie.

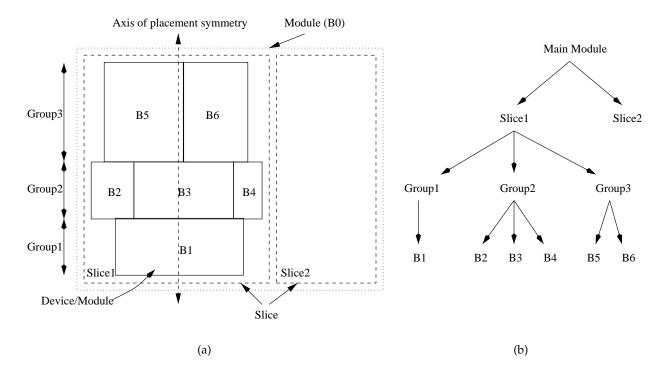

#### 5.2 Hiérarchie et optimisation de la surface

Pendant la construction d'un module, CAIRO suit une méthode de placement hiérarchique, basé sur les arbres de tranches [Conway92]. Pour décrire le placement, les composants élémentaires sont assemblés en groupes, tranches et modules.

Le circuit dans son ensemble doit satisfaire une contrainte sur la hauteur ou sur le facteur de forme. Pour respecter cette contrainte, on utilise un algorithme descendant la hiérarchie qui minimise la surface, voir figure 4. Cet algorithme est hiérarchique, ce qui veut dire que les tranches de niveau supérieur peuvent contenir des sous-circuits existants qui, à leur tour, contiennent plusieurs tranches.

#### 5.3 Extraction des parasites

Après la phase d'optimisation de surface, l'emplacement, la forme et la dimension de chaque composant sont connus avec précision. L'outil CAIRO peut alors calculer les éléments parasites associés à chaque composant de base grâce à un modèle basé sur la géométrie des masques. De même, connaissant précisément la position des composants, de leurs connecteurs et des fils de routage, on peut en déduire aisément les capacités parasites par raport au substrat dues aux fils. Ainsi, dans le mode *calcul des parasites*, tous les élément parasites peuvent être déterminés sans que soient réellement générés les masques physiques.

```

OPTIMIZE\_SLICE(HS)

Phase 1:

FIND the initial set of group heights h<sub>i</sub>;

Phase 2:

DO {

FIND the widest group j (w_j = WS);

FIND \Delta H such that

when h_i = h_i + \Delta H

w_j = f_j(h_j) < WS;

/* Try to compensate \Delta H by the other groups */

FOR each group i \neq j

WHILE (\Delta H > 0)

DO {

h_i = h_i - \Delta h_i such that w_i = f_i(h_i) < WS;

\Delta H = \Delta H - \Delta h_i;

IF (\Delta H \leq 0)

/* \Delta H is compensated by the other groups */

THEN

Conserve the new set of heights;

ELSE

Exit;

};

```

Figure 4: *Algorithme d'optimisation de la surfance*.

## 5.4 L'independance technologique

On a mis au point une variante de l'approche des masques symboliques sur grille fixe [Greiner90]. L'idée directrice de cette approche est que, si les rapports entre largeurs des rectangles et distances bord à bord diffèrent d'une technologies à une autre, les distances entre axes varient de façon quasi homothétique avec la technologie. Les masques sont construits en utilisant des objets appelés symboles, définis soit par un seul point dans le cas des contacts, soit par deux points dans le cas des segments et des transistors. Les symboles sont placés sur une grille isotropique dont les axes sont distants de 1  $\lambda$  dans les deux directions. Par ailleurs, on définit une transformation affine pour calculer les dimensions physiques réelles des masques rectangulaire dans une technologie donnée, à partir des dimensions symboliques et d'un fichier de paramètres technologiques [Greiner95]. On a adapté cette méthode aux masques analogiques en introduisant le placement relatif d'objets déformables et en proposant une bibliothèque de générateurs de composants optimisés. Dans les générateurs de composants élémentaires comme le générateur de transistors ou de capacités, on autorise le placement hors grille symbolique ainsi que les dimensions non entières. En fait, on utilise les règles inverses de la transformation symbolique vers réel pour calculer les dimensons symboliques réelles.

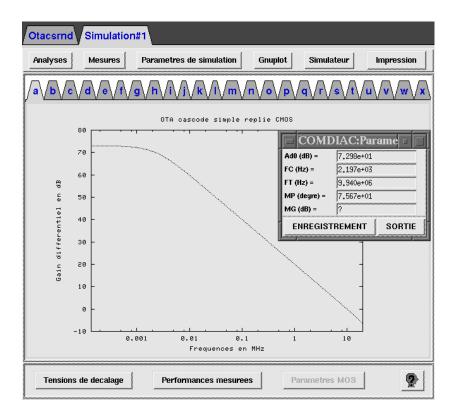

### 6 Dimensionnement d'un circuit en présence de parasites

Les objectifs de l'environnement de synthèse analogique COMDIAC sont doubles : D'une part, l'idée est de faciliter la capture du savoir-faire sous la forme d'un enchaînement d'étapes de synthèse. D'autre part, l'idée est de proposer des procédures de synthèse rapides qui permettent une exploration de l'espace des solutions guidée par le concepteur. COMDIAC offre au concepteur beaucoup de degrés de liberté pour tester diverses solutions.

Le dimensionnement d'un circuit analogique ne peut pas se résumer à une simple procédure algorithmique qui conduirait à une solution unique respectant toutes les spécifications. La philosophie de COMDIAC est d'optimiser une ou deux spécifications les plus essentielles au bon fonctionnement du circuit et de laisser le concepteur fixer d'autres paramètres pour satisfaire au mieux *manuellement* le reste des spécifications. Les estimations que peut fournir COMDIAC sont du même ordre de grandeur que la précision des simulateurs électriques car les modèles des composants sont les mêmes. On utilise une approche hiérarchique qui fait appel au dimensionnement des schémas de base implantés dans COMDIAC. Enfin, on peut choisir indépendamment le modèle de calcul des composants élémentaires, la technologie et la procédure de dimensionnement, ce qui permet de dimensionner un même circuit avec différents modèles et pour différentes technologies.

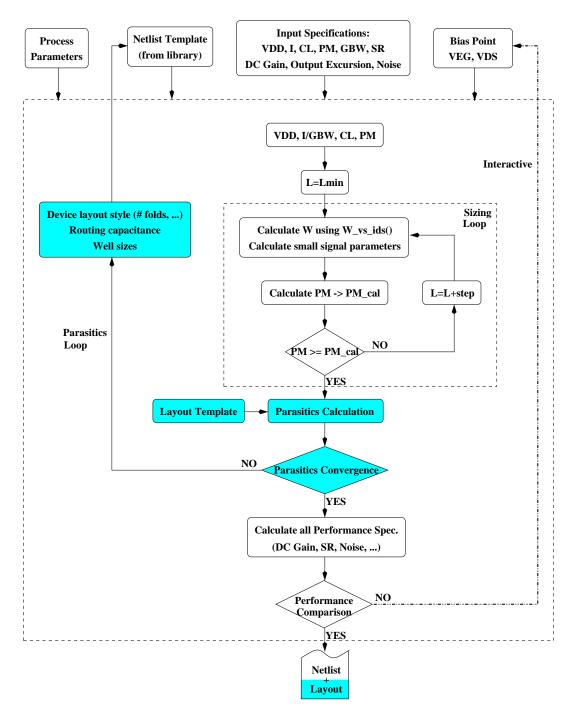

#### 6.1 Exemple de dimensionnement : OTA

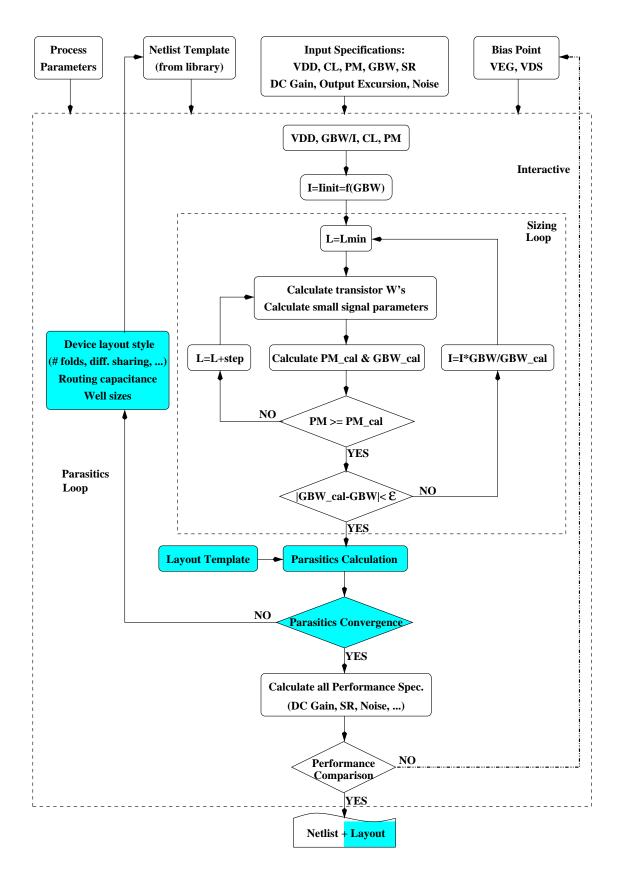

La figure 5 décrit la procédure de synthèse d'un amplificateur implémentée dans COMDIAC. Elle prend en entrée un fichier technologique, un gabarit de netlist, un ensemble de spécifications et la polarisation des transistors. Pour effectuer la synthèse, il faut fixer un premier ensemble de spécifications. On utilise un sous-ensemble des entrées. Il s'agit de :

- la tension d'alimentation V<sub>DD</sub>,

- le courant de polarisation I ou le produit gain-bande GBW,

- la marge de phase PM,

- la capacité de charge *C*<sub>*L*</sub>.

- la polarisation des transistors.

Les tensions de polarisations  $V_{DS}$  et  $V_{EG}$  de chaque transistor sont maintenues constantes dans la boucle de dimensionnement. L'initialisation se fait en fixant les longueurs de tous les transistors à la valeur minimale permise par la technologie. Puis, à chaque itération, on augmente la longueur de chaque transistor, on calcule les largeurs des transistors grâce aux équations analytiques de synthèse et on en déduit les paramètres petits signaux suivant le modèle électrique choisi. La longueur de certains transistors peut être fixée par le concepteur. A la fin de l'itération en cours, on

Figure 5: Procédure de synthèse d'un amplificateur.

calcule la marge de phase. Lorsque la marge de phase souhaitée est atteinte, on appelle l'outil de masques CAIRO pour calculer les éléments parasites associés au circuit. Tant que la convergence des éléments parasites n'est pas obtenue, on rappelle la boucle de dimensionnement en prenant en compte le nombre de repliements des transistors déterminé par CAIRO. Lorsque la conver-

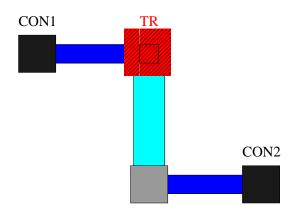

Figure 6: (*a*)*L'interrupteur bootstrap et (b) réalisation en transistors*.

gence des éléments parasites est obtenue, on effectue l'estimation des caractéristiques restantes. Ces caractéristiques peuvent être optimisées d'une manière interactive par le concepteur en choisissant convenablement les tensions de polarisation des transistors. En effet, en fixant le point de polarisation de chaque transistor d'après des considérations sur l'appariement et la dépendance en température, on augmente la fiabilité des circuits réalisés. Le fait que la procédure de dimensionnement soit très rapide et très précise, permet une exploration interactive par le concepteur d'un grand nombre de solutions.

Dans l'environment COMDIAC, notre travail a porté sur l'introduction de la boucle sur les parasites et sur l'introduction de nouvelles prcédures décrites dans les paragraphes suivants.

# 7 Conception d'un circuit à capacités commutées faible tension